Cite as

Nano-Micro Lett.

(2026) 18:180

Received: 24 August 2025

Accepted: 9 November 2025

© The Author(s) 2026

## Oxide Semiconductor for Advanced Memory Architectures: Atomic Layer Deposition, Key Requirement and Challenges

Chi-Hoon Lee<sup>1</sup>, Seong-Hwan Ryu<sup>1</sup>, Taewon Hwang<sup>1</sup>, Sang-Hyun Kim<sup>2</sup>,

Yoon-Seo Kim<sup>1,3</sup> , Jin-Seong Park<sup>1,2</sup>

### HIGHLIGHTS

- This review outlines the emergence of oxide semiconductors as promising channel materials for high-density, low-power next-generation memory applications.

- Adsorption and reaction mechanisms of atomic layer deposition have enabled the design of high-performance oxide semiconductors for next-generation memory applications.

- This review discusses key challenges toward successfully integrating oxide semiconductors into next-generation memory devices.

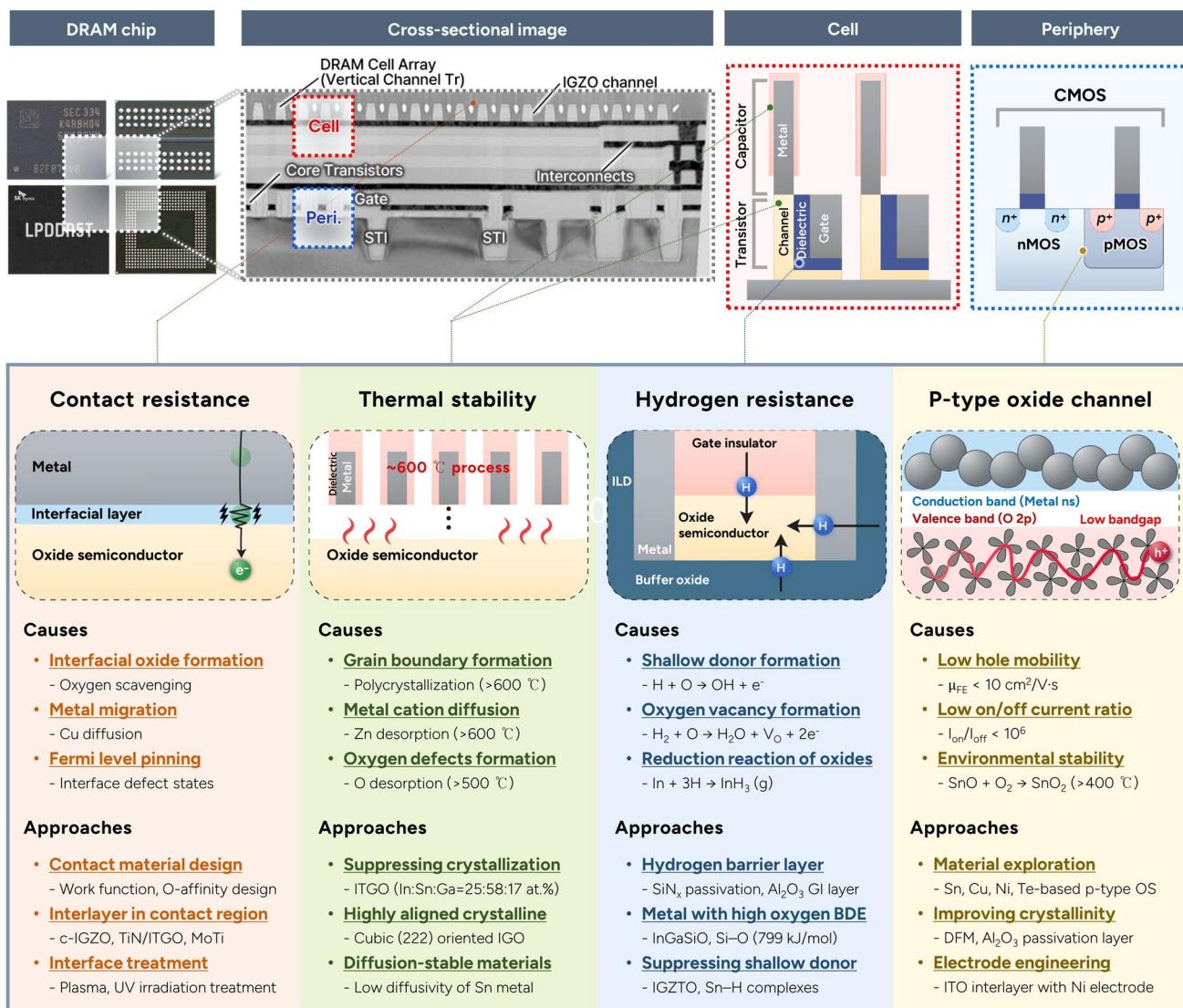

**ABSTRACT** Oxide semiconductors (OSs), introduced by the Hosono group in the early 2000s, have evolved from display backplane materials to promising candidates for advanced memory and logic devices. The exceptionally low leakage current of OSs and compatibility with three-dimensional (3D) architectures have recently sparked renewed interest in their use in semiconductor applications. This review begins by exploring the unique material properties of OSs, which fundamentally originate from their distinct electronic band structure. Subsequently, we focus on atomic layer deposition (ALD), a core technique for growing excellent OS films, covering both basic and advanced processes compatible with 3D scaling. The basic surface reaction mechanisms—adsorption and reaction—and their roles in film growth are introduced. Furthermore, material design strategies, such as cation selection, crystallinity control, anion doping, and heterostructure engineering, are discussed. We also highlight challenges in memory applications, including contact resistance, hydrogen instability, and lack of p-type materials, and discuss the feasibility of ALD-grown OSs as potential solutions. Lastly, we provide an outlook on the role of ALD-grown

Chi-Hoon Lee and Seong-Hwan Ryu have contributed equally to this work.

Yoon-Seo Kim, [yoon-seo.kim@imec.be](mailto:yoon-seo.kim@imec.be); Jin-Seong Park, [jsparklime@hanyang.ac.kr](mailto:jsparklime@hanyang.ac.kr)

<sup>1</sup> Division of Materials Science and Engineering, Hanyang University, 222 Wangsimni-ro, Seongdong-gu, Seoul 04763, Republic of Korea

<sup>2</sup> Department of Display Science and Engineering, Hanyang University, 222 Wangsimni-ro, Seongdong-gu, Seoul 04763, Republic of Korea

<sup>3</sup> Present Address: Imec, Kapeldreef 75, B-3001 Louvain, Belgium

OSs in memory technologies. This review bridges material fundamentals and device-level requirements, offering a comprehensive perspective on the potential of ALD-driven OSs for next-generation semiconductor memory devices.

**KEYWORDS** Oxide semiconductor (OS); Atomic layer deposition (ALD); Memory applications

## 1 Introduction

### 1.1 Beyond Displays: OS Channels for Semiconductor Applications

Advances in modern memory and logic technologies have been driven by continuous scaling down of silicon-based devices. However, this progress is now facing physical limitations of device miniaturization and material limitations related to power consumption [1–4]. Consequently, the need for next-generation channel materials has become increasingly critical. Oxide semiconductors (OSs), well-known in the display industry for their excellent electrical properties and process compatibility, are now attracting growing interest in memory and logic applications [5–7]. Early research focused on their application in back-end-of-line (BEOL) logic technologies, given their capability for deposition on three-dimensional (3D) structures and low-temperature (below 400 °C) processing [8–10]. Recently, OSs have emerged as promising candidates for next-generation memory technologies, driven by demands for reduced cell size, increased transistor density, and vertical channel architectures to enhance integration density [11–13]. The low power consumption of these frameworks renders them especially attractive in dynamic random-access memory (DRAM) applications, where high leakage currents necessitate continuous dynamic refresh operations, leading to significant power consumption [12, 14]. In response to these industrial demands, extensive research is underway for the practical implementation of OS-based devices.

### 1.2 OS Channel Roadmap: From Invention to Mass Production in Displays

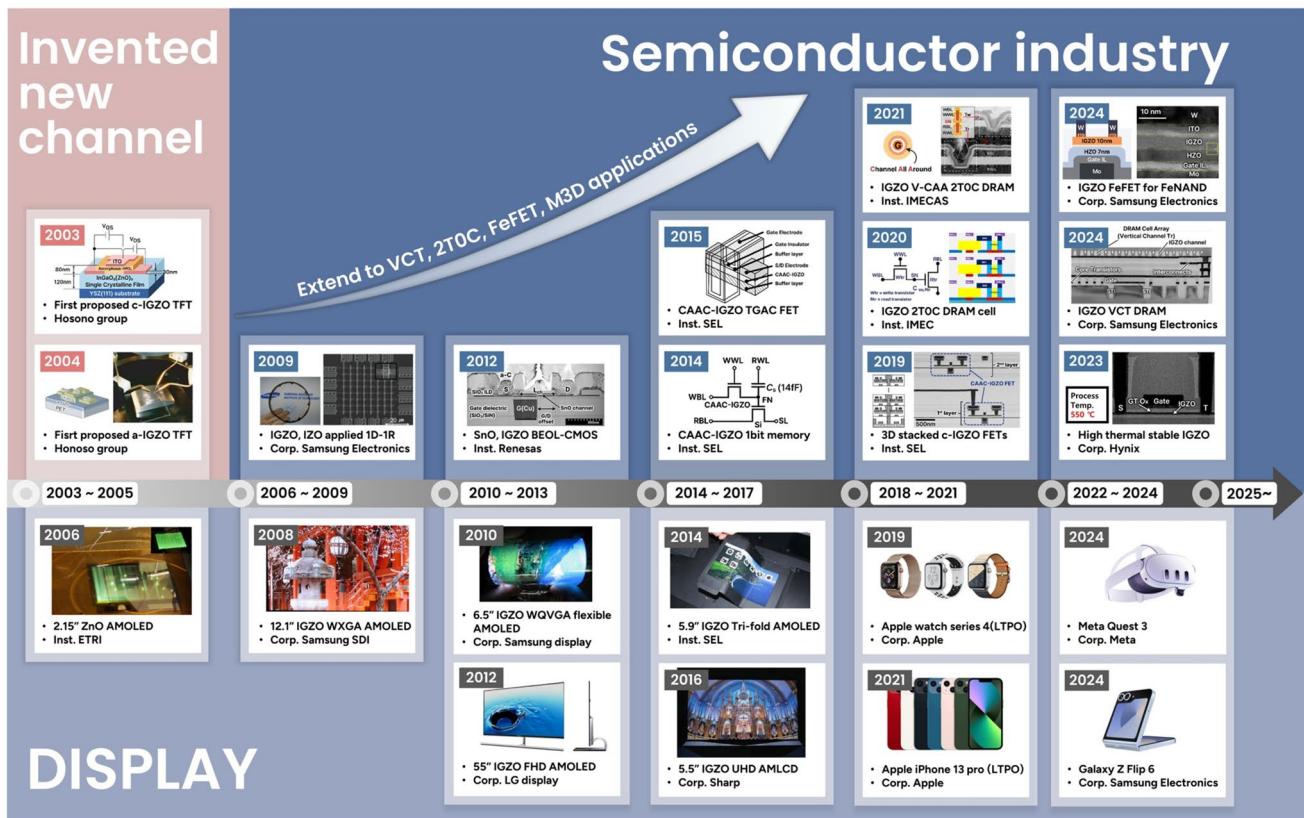

The idea of OSs as next-generation channel materials was first proposed by the Hosono group in 2003 through the demonstration of crystalline InGaZnO (IGZO; light red region in Fig. 1). Specifically, single-crystalline IGZO was synthesized via pulsed laser deposition (PLD) followed by annealing at 1400 °C. When used as the active layer in a

thin-film transistor (TFT), the material exhibited a high field-effect mobility of approximately  $80 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [15]. In 2004, the same group demonstrated the potential of OSs for next-generation displays by fabricating amorphous IGZO (a-IGZO) TFTs on polyethylene terephthalate substrates at room temperature (RT) using PLD and validating their transfer characteristics [16].

Since Hosono's introduction of a-IGZO, OSs have attracted growing interest in next-generation displays due to their low off-state current, high mobility, and low-temperature process compatibility (Fig. 1, light blue region). In 2006, the Electronics and Telecommunications Research Institute, Korea, demonstrated the first active matrix organic light emitting diode (AMOLED) panel using ALD-grown ZnO TFTs [17]. Subsequent milestones include Samsung SDI's 12.1-in AMOLED with sputtered a-IGZO (2008) [18], and Samsung Display's flexible AMOLED (2010) showing robust performance under 10,000 bending cycles [19]. In 2012, LG Display scaled IGZO to Gen. 8 glass for 55-in OLED TVs [20], while SEL introduced a foldable AMOLED using c-axis aligned crystalline indium-gallium-zinc oxide (CAAC-IGZO) in 2014 [21]. Sharp's 1000 ppi IGZO liquid crystal display (LCD) (2016) enabled ultrahigh-resolution displays [22]. Commercial adoption followed, with Apple integrating IGZO into the Apple Watch (2019) and iPhone 13 Pro (2021) [23, 24]. Most recently, IGZO has been adopted in Meta Quest 3 and Samsung Galaxy Z Flip 6 (2024), highlighting its scalability and commercial viability [25].

### 1.3 OS Channel Roadmap for Semiconductor Industrial Applications

As shown in the dark blue region in Fig. 1, research into the application of OSs in the memory and logic industries began expanding in 2009 with Samsung Electronics Inc.'s report on an  $8 \times 8$  one-diode-one-resistor array based on oxide transistors. In this work, IGZO was used to prepare the selector transistor, and indium-zinc oxide (IZO) was applied as the diode. ALD-processed NiO demonstrated

**Fig. 1** Chronological development and technological expansion of oxide semiconductor thin-film transistors (OS-TFTs) from display applications to high-performance memory and logic integration. Starting with the first proposal of IGZO-based TFTs, OS-TFTs were rapidly adopted in display technologies. Subsequently, the application scope has expanded to include advanced logic and memory devices. The images of Apple Watch Series 4 and Apple iPhone 13 Pro were provided by Apple, Inc. The images of Samsung Galaxy Z Flip 6 were provided by Samsung Electronics. Reproduced with permission [15–35]. Copyright 2003, Science. Copyright 2004, Nature. Copyright 2006, 2008, 2009, 2010, 2012, 2014, 2016, 2019, 2024, John Wiley & Sons. Copyright 2012, 2014, 2015, 2019, 2020, 2021, 2023, 2024, IEEE. Copyright 2023, Kim et al.

superior properties compared with sputtered NiO for the resistive element [26]. In 2012, Renesas Corp. demonstrated, for the first time, SnO TFTs exhibiting an  $I_{on}/I_{off}$  ratio over  $10^4$  and a drain voltage capability exceeding 40 V, highlighting the feasibility of SnO and IGZO-based BEOL-complementary metal-oxide semiconductor (CMOS) I/O integration within conventional silicon-based large-scale integration processes [27]. In 2014, SEL Institute realized a novel 50 nm-scale field-effect transistor (FET) employing CAAC-IGZO, reporting excellent device characteristics with a drain-induced barrier lowering (DIBL) of  $67 \text{ mV V}^{-1}$  and a subthreshold swing (SS) of  $92 \text{ mV dec}^{-1}$ . Circuit simulations further demonstrated that memory devices based on this FET architecture could achieve write speeds below 5 ns and retention times exceeding 1000 s [28]. In 2015, SEL reported a scalable, low-cost trench-gate-self-aligned

CAAC-IGZO FET fabricated with only three masks at the 20 nm node, achieving a DIBL of  $0.12 \text{ V V}^{-1}$  and an SS of  $97 \text{ mV dec}^{-1}$  [29]. In 2019, SEL introduced a CAAC-IGZO FET with a gate length of 72 nm integrated into a 3D monolithic stack, fabricated via a trench-gate self-aligned flow at  $\leq 400 \text{ }^{\circ}\text{C}$  with a top-/back-gate effective oxide thickness (EOT) of  $\sim 6 \text{ nm}$  and a back-gate for  $V_{th}$  control ( $-\partial V_{th}/\partial V_{bg} \approx 0.13 \text{ V/V}$ ), with the thermal budget tuned to preserve lower-/upper-device performance. Simulation results indicated the potential for non-volatile OS random-access memory operation featuring write speeds under 10 ns and endurance beyond  $10^{12}$  cycles [30]. In 2020, IMEC Institute reported a world-first capacitor-less two-transistor (2T0C) architecture based on IGZO FETs, built in a 300-mm back-end-of-line (BEOL)-compatible flow using a bottom oxygen-channel stack ( $\text{SiO}_2$  under IGZO with an  $\text{Al}_2\text{O}_3$  top

gate),  $O_2$ -anneal-driven defect passivation, and contact/layout engineering (ALD-TiN to suppress O-scavenging and minimized extension length) to scale the gate-dielectric EOT and boost  $C_{ox}$ , achieving retention times exceeding 400 s without the need for a capacitor [31]. In 2021, IMECAS experimentally demonstrated the world's first vertical channel-all-around (CAA) IGZO FET structure within a 2T0C DRAM cell, built in a BEOL-compatible PEALD flow at  $\sim 250$  °C using  $O_2$  plasma to deposit IGZO/ $Al_2O_3$ /IZO in situ, with Mo/ $SiO_2$ /Mo vertical MIM S/D defining the critical dimension (CD);  $V_{th}$  and SS were optimized by adjusting the  $InO_x:GaO_x:ZnO_x$  cycle ratio and by lowering the plasma power ( $\sim 38$  W), with retention times exceeding 300 s [32]. In 2023, Hynix Corp. confirmed that crystalline IGZO maintained structural stability without agglomeration during a hydrogen-containing high-temperature process at 550 °C—conditions relevant to DRAM fabrication—whereas amorphous IGZO underwent degradation [33]. Most recently, in 2024, Samsung Electronics Inc. proposed a single-gate IGZO-based vertical channel transistor (VCT) structure, DRAM-oriented to suppress passing-gate interference below 10 nm, relocate BL/storage contacts for a 4F<sup>2</sup> cell, favor ALD-IGZO over physical vapor deposition (PVD) for conformal channels with steeper SS and lower  $I_{off}$  at 85 °C, and bias composition toward Ga-rich/low-In to stabilize  $V_{th}$ , overcoming limits of conventional Si-based DRAM and improving scalability [34]. Furthermore, the company demonstrated an oxygen-deficient IGZO-based ferroelectric FET (FeFET), which exhibited a large memory window of 17.8 V and a fast pulse response of approximately 1  $\mu$ s [35]. Overall, the widespread adoption of OSs in display technologies has not only demonstrated their technological significance but also accelerated their exploration for use in next-generation memory applications.

#### 1.4 Growing Attention for OS Channel in Semiconductor Applications

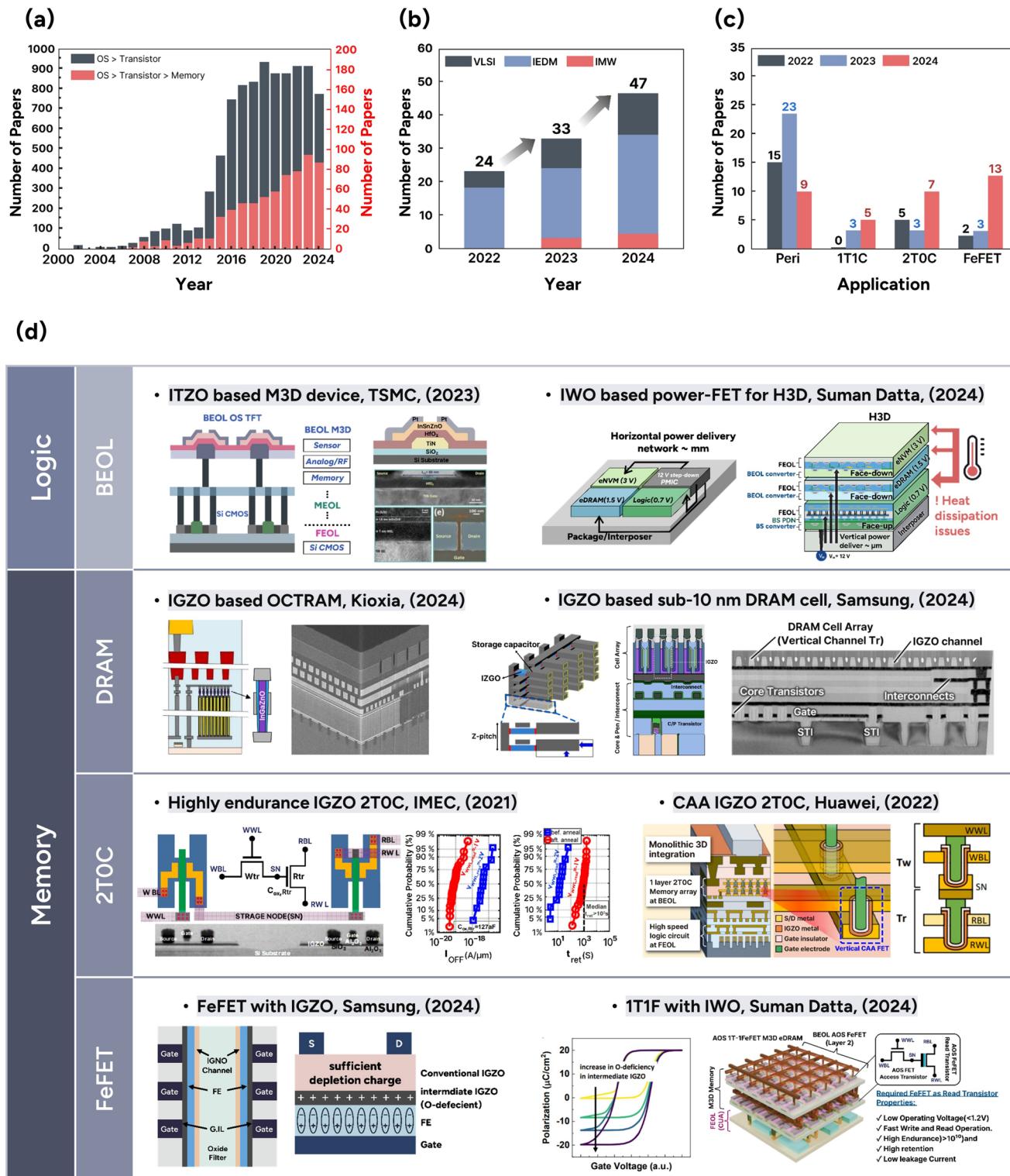

The rising volume of research publications highlights the growing interest in OSs for memory applications. Figure 2a illustrates the chronological increase in the number of publications related to OS devices. The marked acceleration in memory-focused research since 2020 highlights the increasing relevance of OSs in the field. Figure 2b summarizes the number of papers on OSs presented annually at

major international conferences, including the International Memory Workshop (IMW), International Electron Devices Meeting (IEDM), and Symposia on VLSI Technology and Circuits (VLSI). A clear upward trend can be observed from 2022 to 2024, with the total number of papers rising from 24 in 2022 to 47 in 2024, reflecting the expanding attention garnered by this field within the memory and logic industries. Figure 2c categorizes the annual publication count from 2022 to 2024 by application type—BEOL, one-transistor one-capacitor (1T1C), 2T0C, and ferroelectric field-effect transistor (FeFET)—within the memory and logic sectors. While BEOL-related publications increased from 15 in 2022 to 23 in 2023, a decline to 9 was observed in 2024. In contrast, the number of publications related to 1T1C, 2T0C, and FeFET increased to 5, 7, and 13, respectively, in 2024. In other words, although early research on OSs in logic circuits primarily focused on BEOL integration, a recent shift toward their use as core cell transistors in memory applications has been observed. The device benchmarks for each application can be found in Tables 1 and 2 [36–86].

In the evolution of OS-channel-based memory technologies, three cell primitives—1T1C, 2T0C, and FeFET—are drawing significant attention. 1T1C stores charge on a discrete capacitor written/sensed through a gated access path. The defined cell capacitor yields a predictable bit-line signal ( $\Delta V \approx Q/C_{BL}$ ) and controllable retention, while physical separation of the storage node from the channel mitigates disturb and variability, enabling a stable, reproducible memory framework based on destructive read followed by immediate restore [87, 88]. 2T0C is a capacitor-less dynamic cell that separates write/store and read-sense with two transistors, where the parasitic capacitance of read transistor serves as the storage node; removing the capacitor eases BEOL integration and shrinks pitch, with long retention, sensing margin, and variability as key challenges [31, 89]. FeFET embeds a ferroelectric material in the OS gate stack to realize non-volatile, polarization-driven  $V_{th}$  shifts, enabling fast, low-energy operation and analog programmability for in-memory computing [90, 91]. Across these, OS channels are receiving growing attention in next-generation semiconductor development, with sustained academic–industrial efforts.

Recent studies on OS channels for memory and logic applications can be categorized into four types—BEOL, 1T1C, 2T0C, and FeFET—as shown in Fig. 2d. In the context of logic-oriented BEOL integration, from a high-density scaling perspective, in 2023, TSMC Ltd. reported

**Fig. 2** Recent research trends and application landscape of oxide–semiconductor-based devices for logic and memory applications. **a** Annual increase in the number of publications and cumulative citations on oxide semiconductors for memory applications, indicating growing research interest. **b** Yearly distribution of relevant papers across major conferences (IEDM, VLSI, IMW) from 2022 to 2024. **c** Number of published works by application category—back-end-of-line (BEOL), 1T1C, 2T0C, and FeFET—showing increased focus on memory. **d** Representative device demonstrations categorized by application. Reproduced with permission [12, 34, 35, 53, 65, 81, 89, 92]. Copyright 2021, 2022, 2023, 2024, IEEE

**Table 1** Benchmark of OS FETs for BEOL applications (VLSI/IEDM/IMW, 2022–2024)

| OS channel              | Channel thickness (nm) | Process method | Cell architecture | Thermal budget (°C) | $V_{th}$ (V) | $\mu_{FET}$ ( $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ) | S.S (mV dec $^{-1}$ ) | PBS   | $\Delta V_{th}$ (V) | Refs |

|-------------------------|------------------------|----------------|-------------------|---------------------|--------------|-----------------------------------------------------------|-----------------------|-------|---------------------|------|

| $\text{In}_2\text{O}_3$ | 3.1                    | ALD            | GAA               | 250                 | −2.6         | 76–86                                                     | 100                   | −0.7  | [36]                |      |

|                         | 1.9–2.5                | ALD            | Planar            | 300                 | 0.1          | 55                                                        | 150–185               | –     | [37]                |      |

|                         | 1.5–1.8                | ALD            | Planar            | 235                 | 0            | –                                                         | 163                   | –     | [38]                |      |

|                         | 1.5, 2.2               | ALD            | Planar            | 450                 | −1.1         | 107                                                       | 100–150               | –     | [39]                |      |

|                         | 2.5                    | ALD            | Planar            | 225                 | −2.5         | –                                                         | 100                   | −0.07 | [40]                |      |

|                         | 1.3–2.0                | ALD            | Planar            | 225                 | 0            | >100                                                      | –                     | –     | [41]                |      |

|                         | 1.6                    | ALD            | Planar            | 400                 | >0           | 72                                                        | 70                    | 0.03  | [42]                |      |

|                         | 1.2–2.0                | ALD            | Buried-gate       | 290                 | –            | 62                                                        | 100                   | –     | [43]                |      |

|                         | 2.5                    | ALD            | Planar            | 350                 | 0            | 175                                                       | 75                    | –     | [44]                |      |

| $\text{In}_2\text{O}_3$ | 3.5                    | ALD            | Planar            | 250                 | 0            | 45                                                        | 65                    | 0.02  | [45]                |      |

|                         | 2                      | ALD            | Planar            | 300                 | 0.1          | 60                                                        | 69                    | 0.03  | [46]                |      |

| $\text{InGaO}$          | 3                      | ALD            | Planar            | 225                 | 0.4          | 29                                                        | 85                    | 0.03  | [47]                |      |

|                         | 7                      | ALD            | Nanosheet         | 600                 | 0            | 30                                                        | 100                   | 0.1   | [48]                |      |

|                         | –                      | ALD            | Planar            | 250                 | 0            | –                                                         | 75                    | 0.08  | [49]                |      |

|                         | 3                      | ALD            | Planar            | 300                 | 1.2          | 14                                                        | 80                    | –     | [50]                |      |

|                         | –                      | ALD            | Planar            | 450                 | 0            | 20–100                                                    | 68–75                 | –     | [51]                |      |

| $\text{InSnO}$          | 2.9                    | ALD            | Planar            | 400                 | 0.5          | 26                                                        | 95                    | −0.07 | [52]                |      |

|                         | –                      | ALD            | Planar            | 400                 | –            | –                                                         | –                     | –     | [53]                |      |

|                         | 8                      | ALD            | GAA               | 400                 | 0            | 22                                                        | 68–75                 | −0.09 | [54]                |      |

| $\text{InGaZnO}$        | 3.0–4.0                | ALD            | Planar            | 250                 | 0            | 30                                                        | 75                    | 0.12  | [55]                |      |

|                         | 2                      | ALD            | Planar            | 200                 | –            | –                                                         | –                     | 0.5   | [56]                |      |

|                         | 10                     | ALD            | Planar            | 250                 | 0            | 13                                                        | 126                   | –     | [57, 58]            |      |

|                         | 1.5                    | ALD            | Planar            | 250                 | 0            | –                                                         | 68                    | 0.05  | [59]                |      |

|                         | 15                     | ALD            | VCT               | 300                 | 0            | –                                                         | <100                  | –     | [60]                |      |

|                         | 6                      | ALD            | V-GAA             | 400                 | 0.1          | –                                                         | 75–80                 | −0.02 | [61]                |      |

|                         | 5.6                    | ALD            | Planar            | 250                 | 0            | –                                                         | 60                    | −0.1  | [62]                |      |

the implementation of a 1.8-nm ultrathin indium-tin-zinc-oxide film—deposited via ALD—as the channel material in a FET with a 40-nm channel length. This device demonstrated a low DIBL of 22 mV V $^{-1}$  along with a respectable field-effect mobility of 48 cm $^2$  V $^{-1}$  s $^{-1}$  [92]. From a BEOL operational validation and guidance perspective, in 2024, the Suman Datta group investigated the bias-temperature instability (BTI) characteristics of high-voltage W-doped  $\text{In}_2\text{O}_3$  (IWO)-based power FETs designed for heterogeneous 3D (H3D) systems. Using machine learning models, the researchers predicted circuit reliability and proposed thermal optimization strategies, thereby establishing a technological foundation for energy-efficient circuit design in H3D system architectures [53]. Collectively, these findings underscore that BEOL deployment of oxide semiconductors hinges on aligning ALD-enabled device characteristics with thermally

constrained, reliability-aware design practices in stacked architectures.

In the memory industry, OS channels have been actively investigated in the domains of 1T1C, 2T0C, and FeFET, with several recent studies reporting significant advancements. In the 1T1C category, considerable attention has been directed toward the use of the OS channel in VCTs. From an array-level demonstration perspective, in 2024, Kioxia demonstrated the world's first high-density 4F $^2$  DRAM (OCTRAM) featuring a 275 Mbit array, integrating a gate-all-around (GAA) IGZO VCT above a high-aspect-ratio capacitor structure, using a capacitor-first stack to decouple capacitor/VCT interactions and a ~26 nm vertical hole with ALD-IGZO. Device performance was optimized by selecting contact materials to avoid interfacial oxide, thinning the gate oxide and spacer to boost the fringing field,

**Table 2** Benchmark of OS FETs for 1T1C, 2T0C, and FeFET (VLSI/IEDM/IMW, 2022–2024)

| Device category | OS channel | Process method | Cell architecture | $I_{on}$ ( $\mu A \mu m^{-1}$ ) | $S \cdot S$ ( $mV dec^{-1}$ ) | Memory Window <sup>1)</sup> | Retention time (s) | Endurance (cycle) | Multi-level conductance (bit) | Ref  |

|-----------------|------------|----------------|-------------------|---------------------------------|-------------------------------|-----------------------------|--------------------|-------------------|-------------------------------|------|

| 1T1C            | IGZO       | —              | VCT               | >150.0                          | —                             | —                           | 3600               | —                 | —                             | [63] |

| 1T1C            | $In_2O_3$  | PVD            | VCT               | 112.2                           | 84                            | —                           | >100               | —                 | —                             | [64] |

| 2T0C            | IGZO       | ALD            | CAA               | 32.8                            | 92                            | —                           | —                  | —                 | —                             | [65] |

| 2T0C            | IGZO       | ALD            | CAA               | 4.1                             | 109                           | $10^6$                      | 190                | $10^{12}$         | —                             | [66] |

| 2T0C            | IGZO       | ALD            | CFET              | —                               | 135                           | —                           | 200                | 500               | 2                             | [67] |

| 2T0C            | IGZO       | ALD            | CAA               | >3.0                            | 190                           | $>10^6$                     | 100                | $10^{11}$         | —                             | [68] |

| 2T0C            | IGZO       | ALD            | Planar            | >10 $^{-6}$                     | 68                            | —                           | $10^4$             | —                 | 4                             | [69] |

| 2T0C            | IGZO       | ALD            | Planar            | —                               | 65                            | —                           | >5000              | —                 | —                             | [70] |

| 2T0C            | IGZO       | PVD            | Planar            | 1500                            | —                             | —                           | >300               | —                 | 3                             | [71] |

| 2T0C            | IGZO       | PVD            | Planar            | 270                             | 75                            | $10^5$                      | 1000               | —                 | 4                             | [72] |

| 2T0C            | IGZO       | ALD            | CAA               | 0.2                             | 135                           | 25                          | 20                 | —                 | —                             | [73] |

| 2T0C            | IGZO       | PVD            | Planar            | ~4.0                            | —                             | $10^6$                      | 180                | —                 | —                             | [74] |

| 2T0C            | IGZO       | PVD            | Planar            | 24                              | —                             | 5                           | $>10^4$            | —                 | 3                             | [75] |

| 2T0C            | IGZO       | PVD            | Planar            | 10.6                            | 76                            | $10^5$                      | >300               | —                 | 3                             | [76] |

| FeFET           | $In_2O_3$  | ALD            | Planar            | —                               | —                             | 2.5                         | —                  | $>10^9$           | —                             | [77] |

| FeFET           | $In_2O_3$  | ALD            | VCT               | 17                              | 65                            | 1.8                         | >1000              | $>10^9$           | —                             | [78] |

| FeFET           | $In_2O_3$  | ALD            | Planar            | 100                             | 68–105                        | —                           | >1000              | $10^7$            | —                             | [79] |

| FeFET           | IGO        | ALD            | GAA               | —                               | 90                            | 2.5                         | $>104$             | —                 | 2                             | [80] |

| FeFET           | IWO        | ALD            | Planar            | 1                               | 97                            | 1                           | $>104$             | $>10^{12}$        | —                             | [81] |

| FeFET           | IGZO       | ALD            | Planar            | 0.2                             | —                             | >1                          | $>105$             | $>10^{10}$        | —                             | [82] |

| FeFET           | IGZO       | PVD            | Planar            | —                               | —                             | 0.7                         | —                  | $10^7$            | —                             | [83] |

| FeFET           | IGZO       | PVD            | Planar            | ~2                              | —                             | 3.3                         | —                  | $10^{10}$         | —                             | [84] |

| FeFET           | IGZO       | PVD            | Planar            | —                               | —                             | 10                          | >1000              | $10^9$            | 3                             | [85] |

| FeFET           | IGZO       | PVD            | Planar            | ~1                              | —                             | 17.8                        | $10^3$             | $>10^4$           | —                             | [35] |

| FeFET           | IGZO       | PVD            | Planar            | 1.2                             | 62                            | 2.1                         | $>10^8$            | $>10^7$           | —                             | [86] |

<sup>1)</sup>For 2T0C, memory window is defined as  $I_{read}/I_{off}$ . For FeFET, memory window is defined as  $V_{th}^{program} - V_{th}^{erase}$

and applying  $O_2$  anneal with channel-composition tuning to stabilize  $V_{th}$  through BEOL [12]. From a framework/roadmap and process-guidance perspective, in the same year, Samsung Electronics proposed two oxide-based device architectures—an IGZO VCT and a vertically stacked cell array transistor (VS-CAT)—to address the scaling limits of sub-10-nm DRAM technology. Their comparative analysis of PVD and ALD processes for IGZO VCTs highlighted the significance of process optimization, while the use of IGZO in the VS-CAT architecture enabled epitaxy-free stacking without a seed layer, offering advantages such as  $z$ -pitch reduction and process simplification [34]. Collectively, Kioxia's array-level validation and Samsung's framework-level guidance jointly establish both feasibility and a credible technology path for OS channel VCTs as a leading 1T1C DRAM option.

For the 2T0C architecture, research has focused on scaling down devices while improving electrical performance and reliability. From a planar IGZO-2T0C, architecture/integration-validation perspective, in 2021, IMEC Institute demonstrated the 2T0C DRAM operating at a 14 nm channel length using ALD-grown IGZO. Through the adoption of a gate-last integration scheme with a buried oxygen tunnel and careful optimization of the gate dielectric and IGZO channel thickness, the device achieved retention times exceeding  $10^3$  s and endurance beyond  $10^{11}$  cycles [89]. From a vertical CAA IGZO-FET, device-scaling/thermal-reliability perspective, in 2022, Huawei Technologies Co. fabricated the first vertical CAA IGZO FET with a sub-50-nm critical dimension using ALD. PEALD was employed to form conformal IGZO/HfO<sub>x</sub>/IZO ( $\approx 3/8/8$  nm) and defining the  $\sim 55$  nm channel length with a SiO<sub>x</sub> spacer to strengthen electrostatics; the high-k HfO<sub>x</sub> boosted C<sub>ox</sub>, while the stack preserved performance after 300 °C/30 min N<sub>2</sub> anneal and up to 120 °C positive bias temperature stress (PBTS). This device demonstrated high-speed operation ( $I_{on} = 32.8 \mu A \mu m^{-1}$ ), low SS (92 mV dec<sup>-1</sup>), thermal reliability, and compatibility with 2T0C 4F<sup>2</sup> cell architectures—positioning it as a key enabling technology for next-generation ultra-dense, low-latency 3D DRAM [65]. Collectively, these works establish a coherent advancement path for 2T0C, in which planar demonstrations provide array-level validation and integration guidance, and the vertical CAA device platform confirms scalable electrostatics and thermal reliability—jointly de-risking BEOL-compatible processing and paving the way toward ultra-dense 4F<sup>2</sup> DRAM.

In the FeFET domain, recent efforts have emphasized reducing operating voltage, accelerating switching speed, and enhancing endurance. From a stack- and channel-engineering perspective aimed at maximizing the memory window and expediting the roadmap toward vertically integrated, high-density NVM, in 2024, Samsung Electronics Inc. achieved a record-high memory window of 17.8 V in an IGZO-based FeFET by strategically introducing an oxygen-deficient layer within the channel and engineering the gate interlayer. The device exhibited fast switching (1  $\mu$ s), low-voltage operation, and the potential for multi-level signal storage, making it a promising candidate for future high-density non-volatile memory (NVM) [35]. From a BEOL-compatibility and embedded-systems viability perspective—prioritizing ultra-low-voltage operation and exceptional endurance to enable refresh-free 1 T-1FeFET, in 2023, the Suman Datta group developed an amorphous In<sub>2</sub>O<sub>3</sub>-based 1 T-1FeFET device that operated below 0.9 V, with a switching time of 20 ns, endurance over  $10^{12}$  cycles. The potential for refresh-free embedded memory offers a new standard for NVMs in next-generation embedded DRAM and artificial intelligence (AI) accelerators [81]. Collectively, they strengthen the technological foundation linking materials/process innovation to system-level deployability across 3D NVM and energy-efficient embedded memory.

Particularly in AI system development, next-generation NVMs—FeFET, resistive random-access memory (RRAM), and phase change memory (PCM)—are pivotal as enablers of non-volatile on-chip weight storage, substantially reducing data-movement energy. Their multi-level conductance and fast, low-voltage switching enable compute-in/near-memory architectures for analog-like MACs and in situ learning.

In addition to FeFET, OS-channel FETs have been considered for use as selectors in resistive random-access memory (RRAM) or phase change memory (PCM), primarily because they combine low leakage with usable drive at logic-level biases and compatibility with BEOL fabrication. Recent BEOL stacks pair an ITO-engineered IGZO selector ( $I_{on} \approx 196.5 \mu A \mu m^{-1}$ ,  $I_{off} \approx 1 pA \mu m^{-1}$  at  $V_{ds} = 1$  V) with a  $\sim 3.6$ -nm MoS<sub>2</sub> switching layer to realize  $< 1$  V,  $< 100 \mu A$  1T1R operation and vertically stacked 2T0C1R hybrids [93]. Furthermore, sub-10-nm-L<sub>ch</sub> ZnO selectors fabricated at  $\leq 300$  °C deliver record  $I_{on} \approx 561 \mu A \mu m^{-1}$  with sub-pA/ $\mu$ m leakage and have been monolithically integrated with Al<sub>2</sub>O<sub>3</sub>-based RRAM into functional 1T1R arrays,

underscoring OS-selector suitability for dense, energy-efficient crossbars [94].

Across BEOL, 1T1C, 2T0C, and FeFET platforms, high-aspect-ratio vertical channels have become a central focus of investigation. Work on structural design emphasizes precise control of channel geometry, carefully engineered spacer schemes, and conformal, void-free gate fill [95–100]. Efforts in channel-material engineering target composition tailoring, defect suppression, and improved interface passivation [97, 101–105]. Studies on source/drain contacts examine the role of contact interlayers and address resistance asymmetry [106–108]. Collectively, these advances accelerated the maturation of vertical-channel devices for next-generation semiconductor industry.

In summary, OSs continue to attract interest for BEOL integration in logic circuits owing to their low-temperature processability, while their role as core cell transistors in memory devices—particularly in 1T1C, 2T0C, and FeFET architectures—has emerged as a growing area of advanced research.

## 2 Material Fundamentals of OS for Semiconductor Applications

Current semiconductor manufacturing faces interlinked bottlenecks—BEOL thermal budgets, overlay errors, interlayer-via (ILV) pitch limits and interconnect RC overheads, selector/access-device off-state leakage, and scaled contact resistivity—that constrain integration density, and energy efficiency [109–116]. The low-temperature processability of OS channels supports M3D integration, lowering cumulative thermal budget and reducing overlay burden by *in situ* process. Monolithic proximity shortens interconnects and curtails parasitic capacitance, easing ILV pitch pressure and RC delay. In parallel, characteristically low leakage suppresses off-state conduction in selector/access devices, while native n-type behavior promotes electron accumulation at metal contacts without heavy doping or silicide control, reducing specific contact resistivity, in contrast to Si. Taken together, these intrinsic material characteristics indicate that OS channels can directly address several of these pain points.

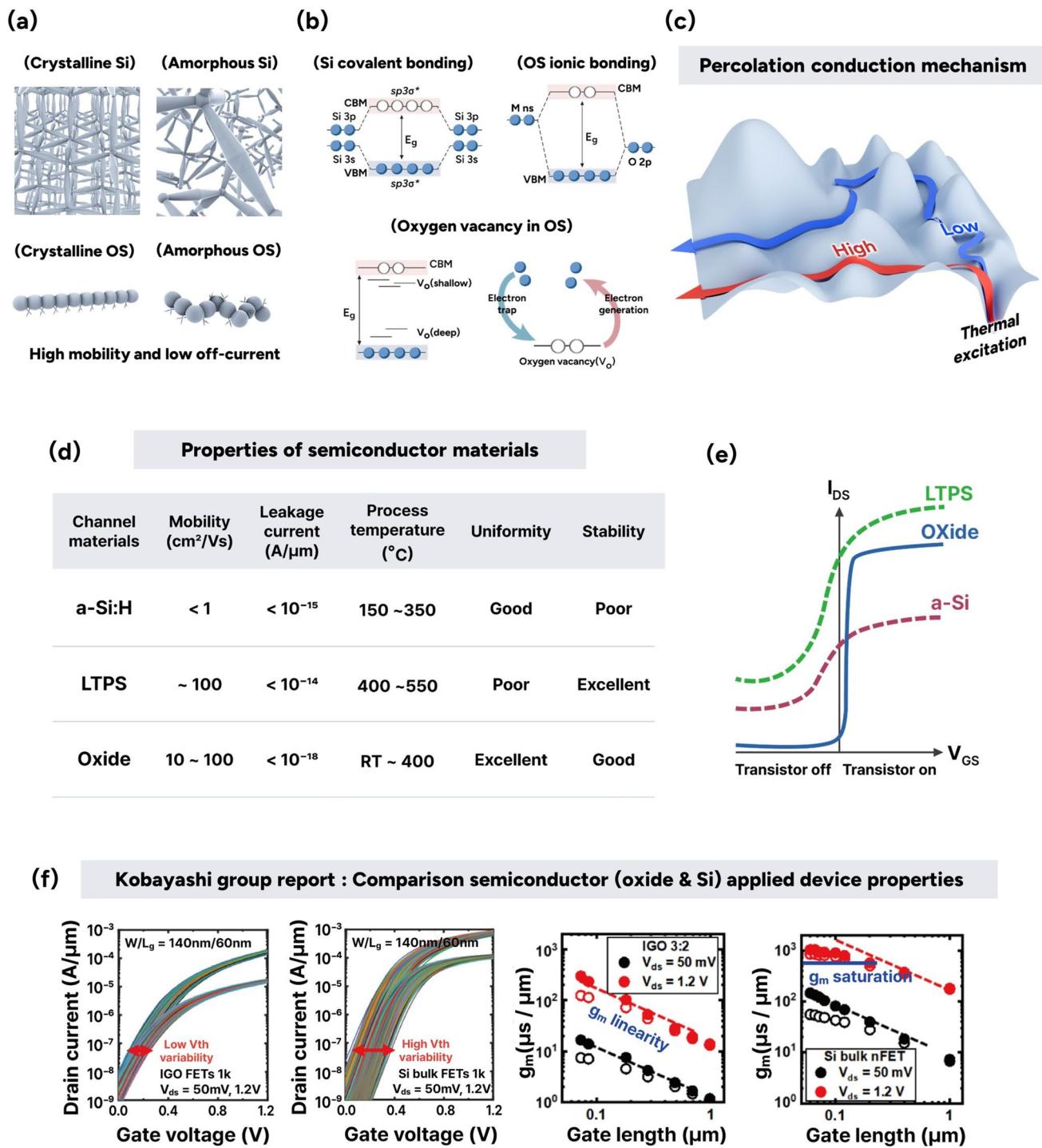

### 2.1 Intrinsic Characteristics of OSs for Semiconductor Applications

The increasing interest in OSs for next-generation memory stems from their distinct electronic band structure, which enables low leakage current, 3D compatibility, and excellent electrical performance, as shown in Fig. 3. As shown in Fig. 3a, OSs maintain high electron mobility in the amorphous phase due to the isotropic and delocalized nature of metal ns orbitals at the conduction band minimum (CBM), enabling efficient charge percolation unlike the directional sp<sub>3</sub> bonding in silicon. The CBM is dominated by metal ns orbitals with large radial extent, yielding a small transport effective mass ( $m^* \approx 0.2\text{--}0.35 m_0$ ) and suppressing band-edge localization despite topological disorder. As shown in Fig. 3b, the ionic bonding in OSs induces a wide bandgap between the O 2p valence band and metal ns CBM, enabling high transparency and low off-state leakage. Despite the large bandgap, oxygen vacancies act as key native defects that donate free electrons, thereby modulating the Fermi level and enabling n-type conductivity [8, 117–119]. These V<sub>O</sub>-related donor states are typically shallow ( $\sim 0.1\text{--}0.3$  eV below the CBM), so even modest thermal or electrostatic modulation can populate the conduction band. As shown in Fig. 3c, OSs exhibit carrier-dependent transport governed by percolation conduction. On this basis, OSs often show a temperature- and density-driven transition from variable-range hopping near the percolation threshold to band-like transport at higher carrier concentrations. In amorphous structures, the disorder creates local potential fluctuations, where free carriers—primarily from oxygen vacancies—facilitate charge transport. These vacancies introduce shallow donor levels that raise the Fermi level toward the CBM, increasing accessible conduction pathways. As the Fermi level nears the CBM, carrier delocalization enhances mobility, especially at higher carrier densities or temperatures, emphasizing the key role of defect chemistry in OS electrical performance [8, 16, 120, 121].

### 2.2 Key Properties of Representative Channel Materials: a-Si:H, LTPS, and OS

Figure 3d compares key properties of representative channel materials, including a-Si:H, LTPS, and OS. a-Si:H enables low-temperature processing (150–350 °C) and good

**Fig. 3** Comparison of structural, electronic, and device-level characteristics of oxide semiconductors (OSs) and silicon-based semiconductors. **a** Schematics of atomic configurations in crystalline and amorphous states for silicon and OSs. **b** Differences in energy band diagrams of Si and OS, including the role of oxygen vacancies. **c** Percolation conduction mechanism in OSs. **d** Comparison of key properties and **e** transfer curves for a-Si:H, LTPS, and OSs. **f** Kobayashi group benchmarking of oxide (IGO) and Si FETs. Reproduced with permission [123]. Copyright 2024, IEEE

uniformity but suffers from low mobility ( $< 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and poor stability. LTPS offers high mobility ( $\sim 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), suitable for high-current applications, but its high crystallization temperature (400–550 °C) limits compatibility, and grain boundaries reduce uniformity across large areas. As shown in Fig. 3e, the high off-current of Si-based semiconductors limits their suitability for low-power memory. In contrast, OSs combine moderate-to-high mobility (10–100  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), ultralow leakage ( $\sim 10^{-18} \text{ A } \mu\text{m}^{-1}$ ), and low-temperature processability (RT–400 °C), making them ideal for display and memory applications [7, 16, 122]. Their steep on–off transitions and low off-currents enhance data retention and reduce refresh power, supporting their use as memory cell transistors.

### 2.3 Benchmarking Report of OS Channel versus Si FETs

Recently, the Kobayashi group made a compelling case for the industrial viability of OS FETs in memory applications by benchmarking them against conventional Si bulk n-channel FETs. Figure 3f illustrates the strategic role of nanosheet OS FETs in enabling monolithic 3D integration, particularly for high-density and energy-efficient memory applications. The figure conceptually depicts the vertical stacking of logic and memory units, where oxide-based access transistors form the foundation of the memory layer directly integrated atop a logic wafer using BEOL-compatible processes. The unique advantages of OSs—high electron mobility, ultralow leakage current, and low-temperature processability—address the stringent requirements of 3D integration that traditional Si-based devices often fail to meet. In particular, recent studies on ALD-grown InGaO FETs have indicated that nanosheet devices with sub-100 nm gate lengths exhibit not only reliable operation at scaled dimensions but also unsaturated carrier velocity even at high fields, unlike conventional Si bulk FETs that exhibit early velocity saturation. This indicates strong potential for high-speed switching in densely packed vertical arrays. Moreover, statistical analyses of over 1000 fabricated nanosheet InGaO FETs reveal tight threshold voltage ( $V_{th}$ ) distributions ( $\sim 20 \text{ mV}$ ), minimal DIBL ( $\sim 18.7 \text{ mV V}^{-1}$ ), and reduced variability in  $I_{on}$  ( $\sim 4.8\%$ ), all of which are comparable or superior to those of foundry-grade Si bulk transistors. These findings underscore the feasibility of OSs in meeting the variability and

reliability requirements for advanced memory-periphery or selector transistors in 1T1C/1T1R arrays [123].

## 3 ALD for OSs: Trends, Fundamentally Engineering, and Advanced Developments

### 3.1 Rising Focus on ALD for OSs in Semiconductor Applications

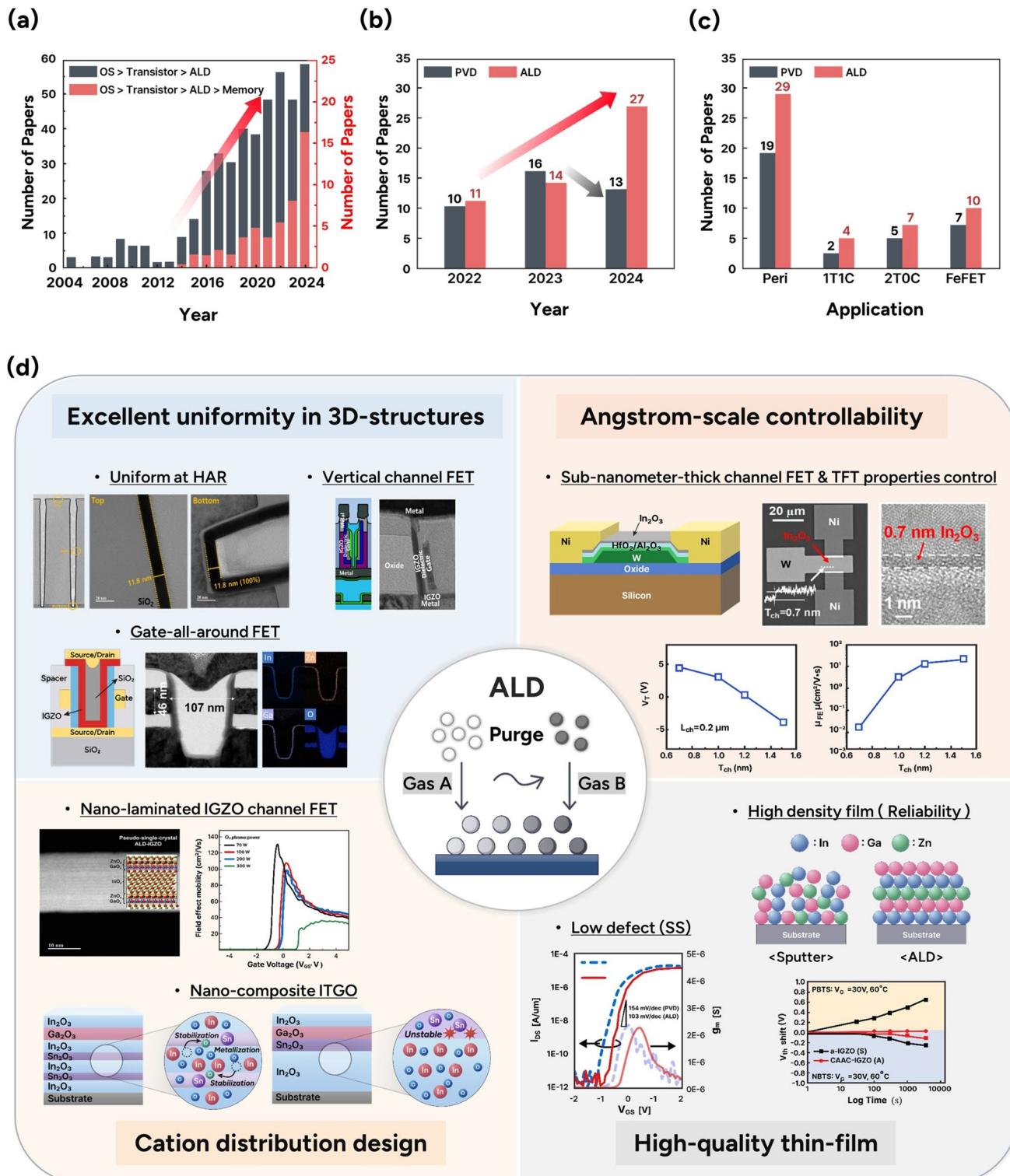

ALD is essential for the integration of OS channels in memory devices. In conventional display applications, PVD has been sufficient to ensure lateral uniformity over large areas in OS TFTs and has been successfully adopted in mass production. However, to apply OS channels to the highly complex 3D architectures found in memory devices, ALD processes with excellent step coverage are required. As shown in Fig. 4a, the number of publications on ALD-based OS FETs has increased significantly since 2014, reaching approximately 60 papers per year in recent years. This upward trend aligns with the growing interest in applications targeting memory devices, which accounted for more than 25% of all ALD-based OS FET publications in 2024. Figure 4b summarizes the number of OS-related presentations categorized by deposition method at major international conferences (IMW, VLSI, and IEDM) over the past three years. The number of PVD-based studies was 10 in 2022, 16 in 2023, and slightly decreased to 13 in 2024. In contrast, ALD-based approaches exhibited rapid growth, increasing from 11 presentations in 2022 to 27 in 2024. Notably, in 2024, ALD-based presentations outnumbered those based on PVD by approximately twice as many presentations. Furthermore, as shown in Fig. 4c, ALD-based OS channel research outpaces PVD across all memory device categories, including peripheral circuits, 1T1C, 2T0C, and FeFET architectures. Considering these trends, research on ALD-based OS channels for memory applications is expected to show continued growth and interest in the coming years.

As shown in the center of Fig. 4d, ALD is a thin-film growth technique based on the sequential injection of self-limiting gaseous precursors and reactants. The increasing adoption of ALD in OS research for memory applications is attributable to four key characteristics: First, ALD offers excellent uniformity in complex 3D structures. In contrast to PVD, which is limited by the directional nature of vapor transport, ALD achieves conformal coating in complex 3D

**Fig. 4** **a** Number of publications from Scopus (search keyword: ALD oxide semiconductor transistor (black column) and memory application (red column)). **b, c** Number of presentations on OSs using PVD and ALD in IMW, VLSI, and IEDM conferences, categorized by year and application. **d** Four key advantages of ALD. Reproduced with permission [34, 61, 125, 128–130]. Copyright 2024, IEEE. Copyright 2020, ACS Publications. Copyright 2022, Springer Nature. Copyright 2023, John Wiley & Sons. Copyright 2024, Elsevier

structures through gas-phase diffusion and self-limiting reactions [34, 124, 125]. Recent emerging 3D DRAM architectures demand conformal deposition techniques in structures with aspect ratios exceeding 20:1. Ryu et al. reported ALD-grown InGaO films (In:Ga=4:1 at%) exhibiting high mobility ( $\sim 128.2 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and thermal stability ( $\sim 700 \text{ }^\circ\text{C}$ ) [126]. To translate this promising channel material into 3D architectures, it is essential to employ a growth technique capable of achieving uniform control over key parameters—such as film thickness, composition, and crystallinity—that critically affect electrical performance. Using ALD, they demonstrated 95% thickness uniformity and less than 1% cation composition variation even in structures with aspect ratios as high as 40:1, while maintaining a uniform crystal structure. These uniform properties of thickness, composition, and crystal structure afford greater flexibility in device architecture design, such as in vertical channel and GAA OS FETs [34, 54, 60, 61].

Second, ALD provides angstrom-level thickness control. The self-limiting nature of the process enables near-monolayer growth per cycle, allowing precise thickness control at the atomic scale [8, 127]. As memory cell sizes continue to scale both laterally and vertically, particularly in vertical channel and GAA structures, thinner channels are required to enhance packing density. Si et al. demonstrated that ALD enables the uniform deposition of  $\text{In}_2\text{O}_3$  channels down to an ultrathin thickness of 0.7 nm [128]. While bulk  $\text{In}_2\text{O}_3$ , with its charge neutrality level located approximately 0.4 eV above the conduction band minimum ( $E_C$ ), is typically considered a conducting oxide, quantum confinement in channels thinner than 1.5 nm can shift the trap neutral level below  $E_C$ , thereby suppressing the carrier density into the semiconducting regime. As the channel thickness directly influences the threshold voltage,  $\text{In}_2\text{O}_3$  can thus be engineered to exhibit clear switching behavior. Such precise thickness control is essential to ensure uniform device characteristics in densely integrated memory arrays.

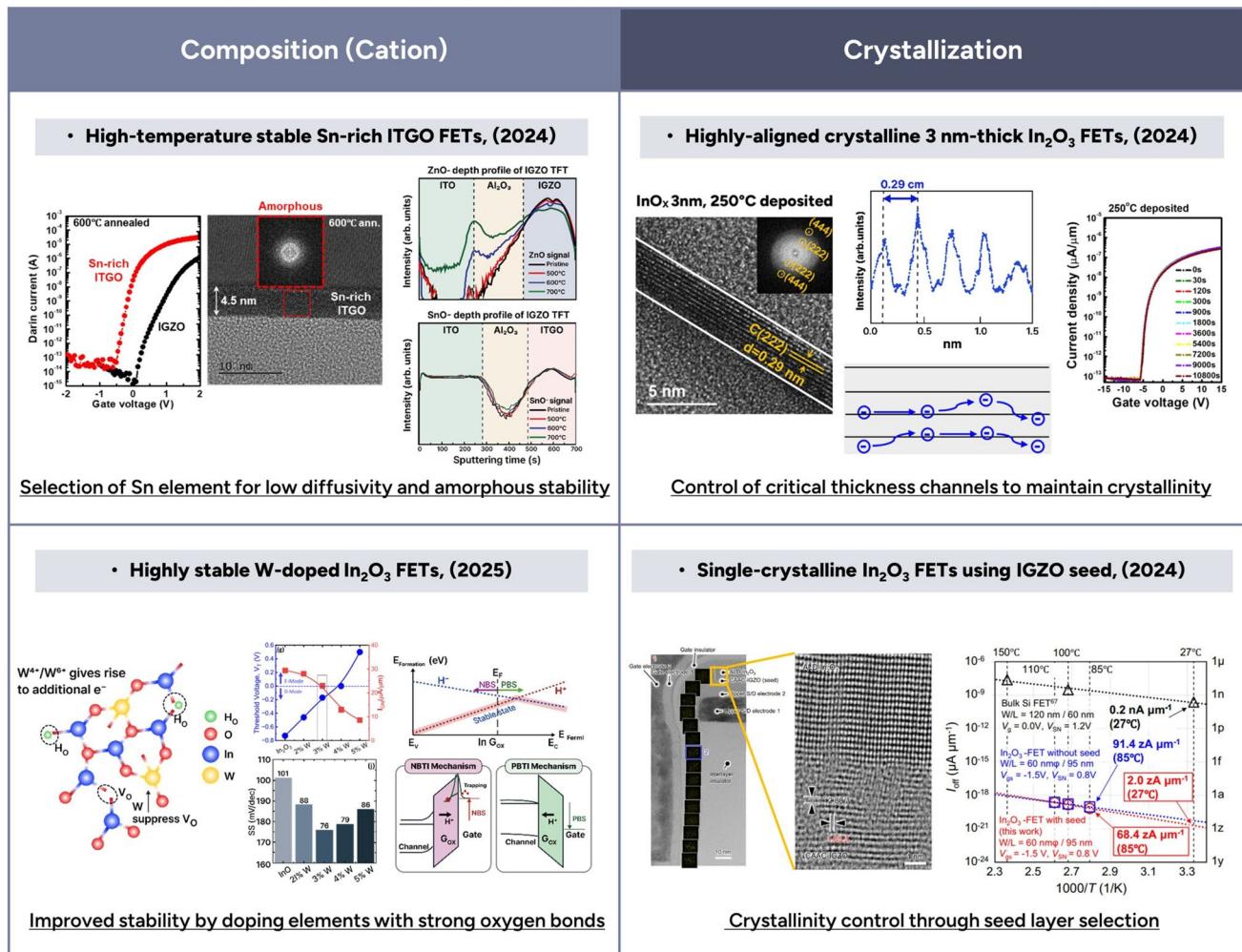

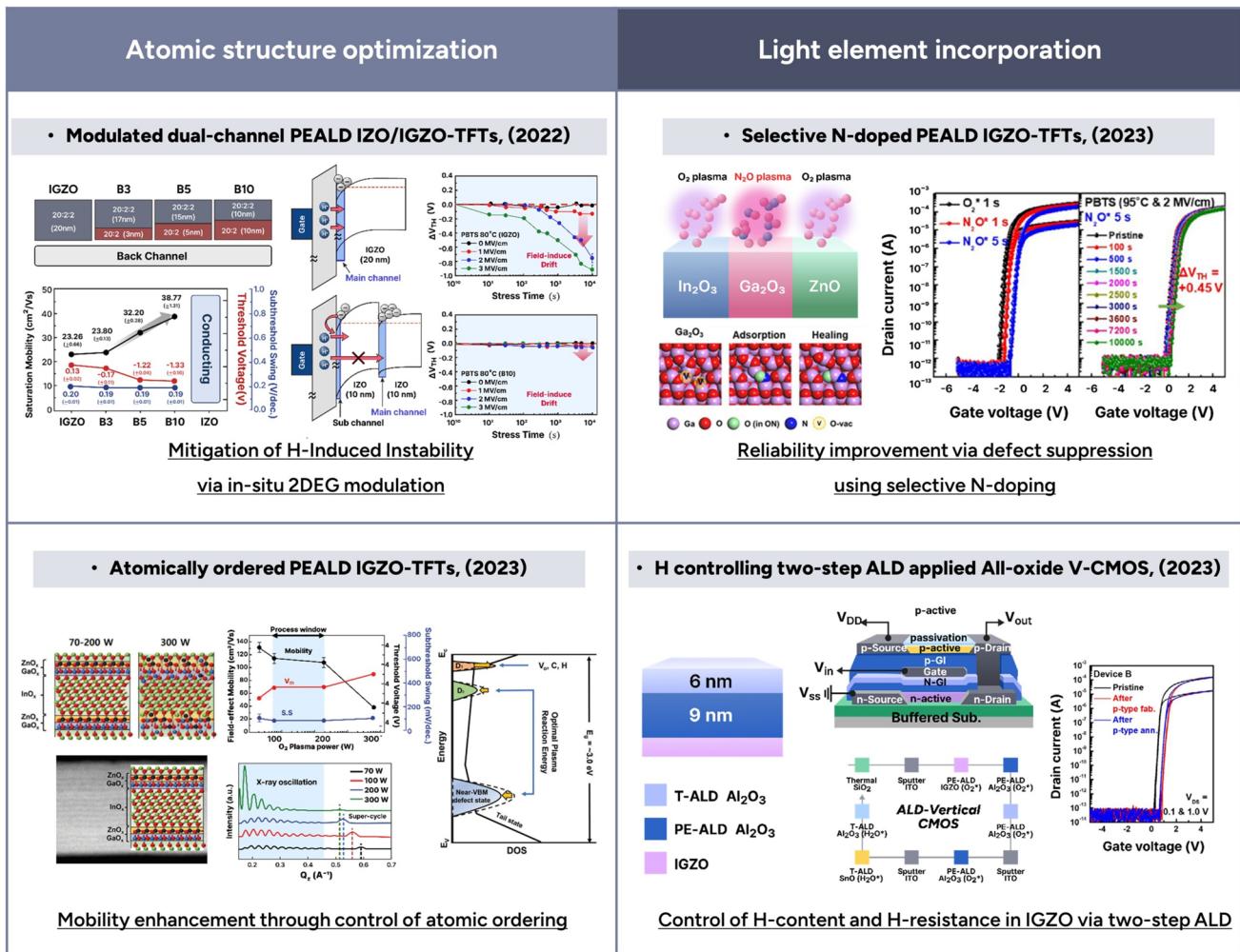

Third, ALD enables the design of cation distribution in multicomponent oxides. The electrical properties of OS materials depend strongly on cation distribution, which can be controlled via sub-cycle modulation in ALD. To meet increasing performance demands in memory applications, OS FETs are expected to achieve higher mobilities ( $> 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and strong reliability under positive bias-temperature stress (PBTS) at elevated temperatures (e.g., 95  $^\circ\text{C}$ ). In a prior study, a nano-laminated

IGZO channel FET was engineered to incorporate  $\text{In}_2\text{O}_3$ , which exhibits high electron conductivity, as the primary conduction path. This design facilitated the formation of multiple 2D electron gas (2DEG) channels, resulting in an enhanced field-effect mobility of approximately  $110 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [125]. In another study, nano-composite  $\text{InSnGaO}$  (ITGO) FETs with homogeneously incorporated Sn cations effectively suppressed oxygen vacancies and improved SS ( $71.9 \rightarrow 64.8 \text{ mV decade}^{-1}$ ) and PBTS reliability ( $\Delta V_{th}; +0.19 \rightarrow 0.06 \text{ V}$  under  $+2 \text{ MV cm}^{-1}$ , 95  $^\circ\text{C}$ , 1 h) [129].

Finally, ALD enables the growth of high-quality thin films. PVD inherently induces structural native defects, as the material is physically removed from the target and directly stacked onto the substrate. In contrast, owing to ALD's layer-by-layer film growth based on self-limiting surface chemical reactions, ALD-based OSs forms close-packed films that effectively minimize impurity incorporation and defect formation compared to other deposition techniques. Owing to its layer-by-layer surface reaction mechanism, ALD minimizes impurity incorporation and defect formation compared to other deposition methods. Kim et al. conducted a comparative study of IGZO films (In:Ga:Zn = 1:1:1 at%) deposited by sputtering and ALD [130]. The ALD-grown IGZO exhibited a reduced concentration of oxygen-related defects (from 34.7 to 24.1%) and improved film density (from 6.01 to 6.30  $\text{g cm}^{-3}$ ). These improvements translated directly into enhanced FET performance, with increases in  $\mu_{FE}$  (from 20.5 to 28.1  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), and reductions in sub-threshold swing (from 0.33 to 0.23  $\text{V decade}^{-1}$ ) and hysteresis (from 0.17 to 0.04 V). Similar improvements in both material and electrical properties have also been reported for other ALD-deposited thin films compared to their PVD counterparts [34, 131]. Given these advantages, research on ALD-based OSs has been actively expanding, with increasing efforts focused on controlling ALD process parameters to optimize electrical performance.

### 3.2 Engineering OSs based on ALD Fundamentals: Adsorption & Reaction

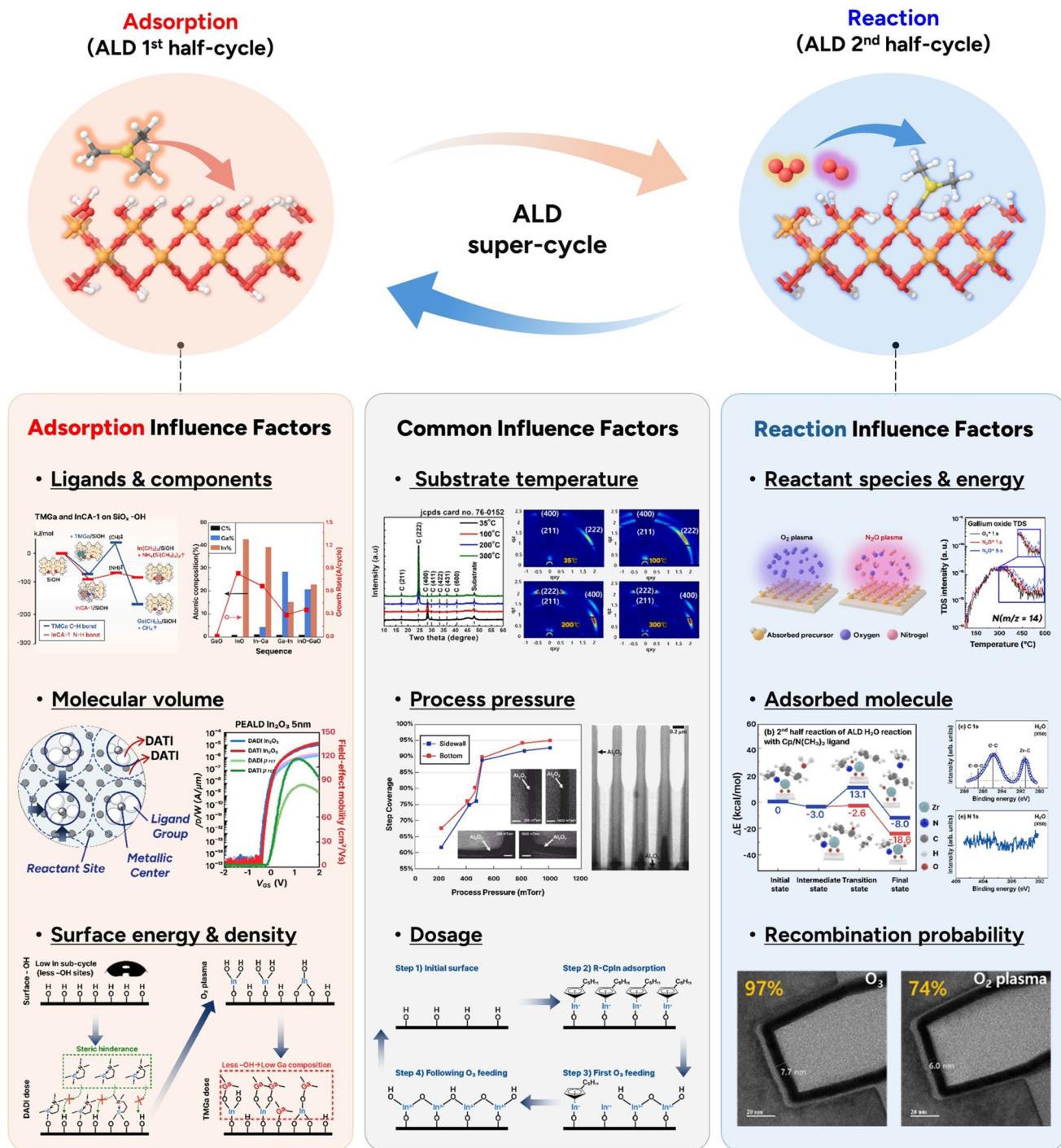

The fundamental principle of ALD pertains to self-limiting chemical reactions, which occur in two key steps: surface adsorption and reaction, as illustrated in Fig. 5. Various process parameters affect each step of the cycle, ultimately

determining the properties of the resulting oxide film. Therefore, a thorough understanding of ALD process variables and their influence on surface reaction behavior is essential for engineering OS channels.

### 3.2.1 Factors Affecting Adsorption (1st Half-Cycle) for OSs Engineering

The first half-cycle of ALD, adsorption, involves the interaction between the precursor and reactive sites on the surface, resulting in the formation of chemisorbed species. This step is the primary consideration when designing both the process and the film properties. As illustrated in the adsorption influence factors shown in Fig. 5, several key parameters affect this process. First, the types of precursor ligands and metal components play a critical role. The adsorption energy ( $\Delta E_{\text{ads}}$ ) and activation energy ( $E_a$ ) of the surface reaction vary depending on the metal center and ligand structure of the precursor. These factors determine whether adsorption occurs and which pathway is preferred. As adsorption reactions are generally associated with a reduction in entropy ( $\Delta S < 0$ ), the spontaneity of the reaction can be assessed based on the sign of  $\Delta E_{\text{ads}}$ : A negative  $\Delta E_{\text{ads}}$  indicates a spontaneous process, while a positive value suggests a non-spontaneous reaction, providing insights into the suitability of a precursor for ALD applications [132, 133]. Among multiple spontaneous adsorption pathways, the one with the lowest  $E_a$  dominates, and this information can help predict both the reaction mechanism and configuration of the adsorbed species [134, 135]. Sheng et al. employed density functional theory to calculate the adsorption energy profiles of an In precursor, diethyl[1,1,1-trimethyl-N-(trimethylsilyl)-silanaminato]-indium (InCA-1), and a Ga precursor, trimethylgallium (TMGa), on a  $\text{SiO}_2$  substrate [132]. Both precursors exhibited negative adsorption energies— $\Delta E_{\text{ads}} = -90.6 \text{ kJ mol}^{-1}$  for InCA-1 and  $-72.1 \text{ kJ mol}^{-1}$  for TMGa—indicating favorable adsorption for ALD. However, the  $E_a$  for TMGa was significantly higher ( $\sim 100 \text{ kJ mol}^{-1}$ ) compared to that of InCA-1 ( $14.5 \text{ kJ mol}^{-1}$ ), suggesting a kinetic limitation that hinders initial growth. These findings highlight the importance of precursor-specific kinetics and were utilized to optimize sub-cycle sequencing for effective film growth and compositional control in multicomponent IGO systems.  $E_a$  also defines the energy barrier: an increase in substrate temperature leads to a higher reaction

probability and improves reaction completion. Thus,  $E_a$  ultimately determines the minimum substrate temperature at which adsorption begins [136]. When the second half-cycle is sufficiently reactive, the ALD temperature window can be affected by the ligand structure of precursors, as summarized in Table 3 [137–175]. Choi et al. reported that an amine ligand-based In precursor, dimethyl[N-(tert-butyl)-2-methoxy-2-methylpropan-1-amine] indium (DMION), enables a reduction of the ALD window lower limit to  $35^\circ\text{C}$ , compared to conventional alkyl ligand-based In precursors [149]. This low-temperature process yielded high-quality, carbon-free ( $< 0.1 \text{ at\%}$ ) films, and the resulting material demonstrated viable FET operation, with a  $V_{\text{th}}$  of  $4.9 \text{ V}$  and  $\mu_{\text{FE}}$  of  $3.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . These results indicate that the target process temperature can be tailored by modifying the ligand structure. In addition, precursor behaviors such as decomposition, condensation, and desorption must be carefully considered for optimal process design.

Second, the molecular volume of the precursor considerably affects adsorption. Even if a certain adsorption pathway is thermodynamically favored, steric hindrance can prevent the precursor from accessing all surface reactive sites. As the volume of the adsorbed species increases, steric limitations become more severe, which reduces the number of precursor molecules that can adsorb per cycle, resulting in a lower growth per cycle (GPC). For example, Oh et al. compared the ALD behavior of trimethylaluminum (TMA) and triethylaluminum (TEA) based on their molecular sizes [176]. The effective average molecular volumes were  $87.2 \text{ \AA}^3$  for TMA and  $140.2 \text{ \AA}^3$  for TEA, with the larger TEA molecule exhibiting a reduced GPC of  $0.8 \text{ \AA cycle}^{-1}$ , compared to  $1.2 \text{ \AA cycle}^{-1}$  for TMA. Similarly, in the ALD of crystalline  $\text{In}_2\text{O}_3$ , the use of a smaller-volume precursor, (N,N-dimethylbutyl-amine)trimethylindium (DATI), led to enhanced adsorption coverage, resulting in improved film density ( $6.57 \rightarrow 6.76 \text{ g cm}^{-3}$ ), crystallinity, and  $\mu_{\text{FE}}$  ( $90.5 \rightarrow 115.8 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), compared to a larger precursor, (3-(dimethylamino)propyl)-dimethyl indium (DADI) [177]. In multicomponent systems, larger dopant precursors have been found to promote more homogeneous doping. For example, homogeneous cation distributions in crystalline  $\text{InGaO}$  improve grain alignment and  $\mu_{\text{FE}}$  ( $\sim 128.2 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) upon crystallization [126], while in amorphous  $\text{AlZnO}$  systems, reduced electron scattering leads to enhanced conductivity [178]. These findings suggest that controlling adsorption behavior through molecular volume design of precursors is an effective strategy for

**Fig. 5** Overview of ALD process parameters for Oxide Semiconductors: Factors influencing the adsorption step, reaction step, and both adsorption and reaction. Reproduced with permission [132, 147, 149, 177, 192, 193, 200, 210]. Copyright 2017, 2021, 2023 ACS Publications. Copyright 2022, 2023, 2024, Elsevier. Copyright 2007, The Electrochemical Society

tuning the structural and electrical properties of thin films [126, 176–178].

Finally, surface energy and the density of reactive sites also strongly influence adsorption. Surface energy depends on various factors, such as substrate type and orientation,

**Table 3** ALD process information for  $\text{InO}_x$ ,  $\text{GaO}_x/\text{ZnO}_x$ , and  $\text{SnO}_x$ , and the material properties

| Precursor                | Reactant                        | Growth Temperature (°C)         | GPC (Å cycle <sup>-1</sup> ) | Impurity 1) (%)   | $E_g$ (eV) | Crystallinity         | Hall mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | TFT mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Refs  |

|--------------------------|---------------------------------|---------------------------------|------------------------------|-------------------|------------|-----------------------|------------------------------------------------------------------|-----------------------------------------------------------------|-------|

| Indium oxide             | TMIn                            | $\text{H}_2\text{O}/\text{O}_2$ | 100–250                      | 0.2–1.6           | –          | –                     | 38–111                                                           | –                                                               | [137] |

|                          | Ozone                           | 100–200                         | 0.46                         | C~1.5 at%         | 3.6        | –                     | ~50                                                              | –                                                               | [138] |

| TMIn                     | Ozone                           | 100–250                         | 0.6                          | –                 | 3.8        | Cubic>200 °C          | –                                                                | –                                                               | [139] |

| TMIn                     | $\text{H}_2\text{O}/\text{O}_2$ | 100–250                         | 1.5                          | –                 | –          | Cubic>200 °C          | ~49                                                              | –                                                               | [140] |

| TMIn                     | Ozone                           | 200–450                         | 0.3–2.0                      | –                 | –          | Cubic>140 °C          | –                                                                | –                                                               | [141] |

| TMIn                     | $\text{ArO}_2$ radical          | 100–400                         | 0.14                         | C                 | 3.6        | Cubic at 275 °C       | –                                                                | –                                                               | [142] |

| TMIn                     | $\text{H}_2\text{O}$            | 165–200                         | 0.2                          | –                 | –          | Cubic>100 °C          | –                                                                | –                                                               | [143] |

| TMIn                     | Ozone                           | 165–225                         | 0.12                         | –                 | –          | –                     | –                                                                | –                                                               | [143] |

| TMIn                     | $\text{H}_2\text{O}$            | 150–250                         | 0.1–0.3                      | N/D               | 3.7        | –                     | ~41                                                              | –                                                               | [144] |

| TEIn                     | Ozone                           | 100–250                         | 0.8                          | –                 | 3.9        | Cubic>200 °C          | –                                                                | –                                                               | [139] |

| InCp                     | $\text{H}_2\text{O}$            | 175–275                         | 0.7                          | Si, C             | 3.9        | Cubic>200 °C          | –                                                                | –                                                               | –     |

| –                        | $\text{H}_2\text{O}_2$          | 125–225                         | 0.7                          | Si, C             | 4          | Cubic>200 °C          | –                                                                | ~15                                                             | [145] |

| In(tmhd) <sup>3</sup>    | Ozone                           | 150–300                         | 0.7                          | N/D               | 3.6        | Cubic>200 °C          | ~51.8                                                            | –                                                               | [139] |

| In(acac) <sup>3</sup>    | $\text{H}_2\text{O}$            | >275                            | 0.6                          | \$text{C>1 at%}\$ | 3.6        | Cubic>200 °C          | –                                                                | –                                                               | [146] |

| Me <sub>2</sub> In(edpa) | $\text{ArO}_2$ plasma           | 100–250                         | 0.8                          | N/D               | 3          | Cubic>275 °C          | –                                                                | ~10                                                             | [147] |

| InCA <sup>-12</sup> )    | $\text{H}_2\text{O}$            | 100–250                         | 0.2                          | C                 | 3          | Cubic>100 °C          | ~1.0                                                             | ~6.1                                                            | [148] |

| DADI <sup>3</sup>        | –                               | –                               | –                            | –                 | –          | Rhombohedral<200 °C   | –                                                                | –                                                               | –     |

| –                        | –                               | –                               | –                            | –                 | –          | Cubic>200 °C          | –                                                                | –                                                               | –     |

| TMION <sup>4</sup>       | $\text{ArO}_2$ plasma           | 100–250                         | 1.1                          | N/D               | 3.4        | Cubic>100 °C          | ~5.1                                                             | ~20.6                                                           | [147] |

| –                        | $\text{ArO}_2$ plasma           | 35–300                          | 1.2                          | N/D               | 3.4        | Cubic>35 °C           | ~5<100 °C                                                        | ~3.1<100 °C                                                     | [149] |

| DMION <sup>4</sup>       | –                               | –                               | –                            | –                 | –          | –                     | ~33>100 °C                                                       | ~34.4>100 °C                                                    | –     |

| DMITN <sup>4</sup>       | $\text{H}_2\text{O}$            | 200–250                         | 0.3                          | N/D               | 3.3        | Cubic>200 °C          | ~2                                                               | –                                                               | [150] |

| DATI <sup>3</sup>        | $\text{ArO}_2$ plasma           | 100–250                         | 1.1                          | N/D               | 3.5        | Cubic>100 °C          | ~9                                                               | –                                                               | [151] |

| Indium oxide             | $\text{ArO}_2$ plasma           | 100–250                         | 1                            | N/D               | 3.4        | Cubic>100 °C          | ~1.1                                                             | ~17.5>250 °C                                                    | [166] |

| TDMASn                   | $\text{H}_2\text{O}$            | 30–200                          | 0.3–2.0                      | N/D               | 3.6–4.0    | Tetragonal            | –                                                                | –                                                               | [167] |

| Tin oxide                | BDMADMSn                        | Ozone                           | 50–250                       | 0.98–1.60         | N/D        | 2.9–4.0               | Tetragonal                                                       | ~32                                                             | –     |

|                          |                                 | $\text{ArO}_2$ plasma           | 100–250                      | ~1.25             | N/D        | 3.6                   | Tetragonal                                                       | –                                                               | [168] |

|                          |                                 | Ozone                           | 150–250                      | ~0.49             | N/D        | –                     | Tetragonal                                                       | ~2.7                                                            | [169] |

|                          |                                 | $\text{H}_2\text{O}_2$          | 250                          | 1.22–1.38         | –          | 3.6                   | Tetragonal                                                       | ~9.9                                                            | [170] |

| SnCl <sub>4</sub>        | –                               | –                               | –                            | –                 | –          | –                     | –                                                                | –                                                               | [171] |

| HS-                      | $\text{H}_2\text{O}_2$          | 60–150                          | 0.1–0.5                      | N/D               | ~1.6       | Tetragonal (> 100 °C) | ~18                                                              | ~6.0 (p-type)                                                   | [172] |

| Stannylene-01            | Ozone                           | 80–250                          | ~1.4                         | N/D               | ~4.1       | Tetragonal            | ~24                                                              | –                                                               | [172] |

| Sn(edpa) <sup>2</sup>    | $\text{ArO}_2$ plasma           | 60–300                          | 0.2                          | N/D               | ~2.9       | –                     | –                                                                | –                                                               | [173] |

| Sn(dmamp) <sup>2</sup>   | $\text{H}_2\text{O}$            | 175–275                         | –                            | N/D               | ~4.0       | Tetragonal (> 70 °C)  | ~27                                                              | –                                                               | [173] |

|                          | Ozone                           | 100–230                         | 0.18–0.42                    | N/D               | 3.6        | Polycrystalline       | –                                                                | ~7.24                                                           | [174] |

|                          |                                 | –                               | –                            | –                 | –          | Tetragonal            | –                                                                | –                                                               | [175] |

Table 3 (continued)

| Precursor                                        | Reactant                      | Growth Temperature (°C) | GPC (A° cycle <sup>-1</sup> ) | Impurity 1 (%) | $E_g$ (eV) | Crystallinity | Hall mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | TFT mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Refs  |

|--------------------------------------------------|-------------------------------|-------------------------|-------------------------------|----------------|------------|---------------|------------------------------------------------------------------|-----------------------------------------------------------------|-------|

| Gallium oxide                                    | Ga(acac) <sup>3</sup>         | Ozone                   | 150–300                       | 0.16–0.54      | N/D        | 4.5           | –                                                                | –                                                               | [152] |

|                                                  | TMGON                         | ArO <sub>2</sub> plasma | 150–250                       | 0.75–1.30      | N/D        | 4.6–4.8       | –                                                                | –                                                               | [147] |

| DMGON                                            | Ozone                         | 250                     | 0.62                          | N/D            | 4.5        | –             | –                                                                | –                                                               | [153] |

| DMGTN                                            | ArO <sub>2</sub> plasma       | 365–380                 | 0.33                          | –              | –          | –             | –                                                                | –                                                               | [154] |

| GTIP                                             | Ozone                         | 350–375                 | 0.22                          | –              | –          | –             | –                                                                | –                                                               | [154] |

| Ga(tmhd) <sup>3</sup>                            | ArO <sub>2</sub> plasma       | 100–250                 | 1.05                          | C~1.2 at%      | –          | –             | –                                                                | –                                                               | [146] |

| Ga <sub>2</sub> (NMe <sub>2</sub> ) <sup>6</sup> | Ozone                         | 150–300                 | 0.11–0.46                     | N/D            | –          | –             | –                                                                | –                                                               | [126] |

| Gal <sub>3</sub>                                 | ArO <sub>2</sub> plasma       | 100–250                 | 0.92–1.32                     | N/D            | 5.2        | –             | –                                                                | –                                                               | –     |

| TEGa                                             | H <sub>2</sub> O              | 150–300                 | 0.10–0.40                     | N/D            | –          | –             | –                                                                | –                                                               | –     |

| TMGa                                             | ArO <sub>2</sub> plasma       | 100–400                 | 1.17                          | N/D            | 5.2        | –             | –                                                                | –                                                               | [155] |

|                                                  | H <sub>2</sub> O              | 150–250                 | 2.5                           | N/D            | ~5.4       | –             | –                                                                | –                                                               | [156] |

| DEZ                                              | ArO <sub>2</sub> plasma       | 60–160                  | 0.1                           | N/D            | 5          | –             | –                                                                | –                                                               | [157] |

|                                                  | Ozone                         | 150–550                 | 0.9–1.1                       | C~2.1 at%      | –          | –             | –                                                                | –                                                               | [158] |

|                                                  | H <sub>2</sub> O <sub>2</sub> | 100–200                 | 1.5                           | I~3.2 at%      | –          | –             | –                                                                | –                                                               | [159] |

|                                                  | Ozone                         | 100–200                 | 0.5–1.75                      | –              | 4.9        | –             | –                                                                | –                                                               | [160] |

|                                                  | H <sub>2</sub> O              | 150–300                 | ~1.50                         | N/D            | 3.2        | Hexagonal     | ~10                                                              | –                                                               | [160] |

|                                                  | ArO <sub>2</sub> plasma       | 100–200                 | ~1.58                         | N/D            | 3.2        | Hexagonal     | ~11                                                              | –                                                               | [161] |

|                                                  | Ozone                         | 150–300                 | ~1.61                         | N/D            | 3.2        | Hexagonal     | ~3.0                                                             | –                                                               | [162] |

| Zn(DMP) <sub>2</sub>                             | ArO <sub>2</sub> plasma       | 100–250                 | 1.57–1.70                     | (> 200 °C)     | 3.2        | Hexagonal     | –                                                                | –                                                               | [163] |

| DEZDMEA                                          | H <sub>2</sub> O              | 150–250                 | 0.9                           | N/D            | 3.2        | Hexagonal     | –                                                                | 0.04                                                            | [164] |