### Cite as

Nano-Micro Lett.

(2026) 18:188

Received: 4 October 2025

Accepted: 29 November 2025

© The Author(s) 2026

# Self-Rectifying Memristors for Beyond-CMOS Computing: Mechanisms, Materials, and Integration Prospects

Guobin Zhang<sup>1,2,3,4</sup>, Xuemeng Fan<sup>1,3,4</sup>, Zijian Wang<sup>1,3,4</sup>, Pengtao Li<sup>1,2,3,4</sup>,

Zhejia Zhang<sup>1,3,4</sup>, Bin Yu<sup>1</sup>, Dawei Gao<sup>1,3,4</sup>, Desmond Loke<sup>6</sup>, Shuai Zhong<sup>5</sup> ,

Qing Wan<sup>2</sup> , Yishu Zhang<sup>1,2,3,4</sup>

## HIGHLIGHTS

- SRMs integrate intrinsic diode-like rectification, enabling sneak path suppression in crossbar arrays without external selectors, simplifying design, and enhancing energy efficiency for high-density in-memory computing.

- Key metrics such as rectification ratio, nonlinearity, and CMOS compatibility are systematically reviewed, highlighting progress in 3D integration and scalable array.

- Applications span in-memory computing, neuromorphic networks, and hardware security, with emerging potentials in in-sensor computing and self-supervised learning, positioning SRMs as pivotal beyond-CMOS building blocks.

**ABSTRACT** The deceleration of Moore's law and the energy–latency drawbacks of the von Neumann bottleneck have heightened the pursuit for beyond-CMOS designs that integrate memory and compute. Self-rectifying memristors (SRMs) have emerged as promising building blocks for high-performance, low-power systems by combining resistive switching with intrinsic diode-like behavior. Their unidirectional conduction inhibits sneak-path currents in crossbar arrays devoid of external selectors, while nonlinear  $I$ – $V$  characteristics, adjustable conductance states, low operating voltages, and rapid switching facilitate efficient vector–matrix operations, neuromorphic plasticity, and hardware security primitives. This review synthesizes the working mechanisms of SRMs, surveys material, and structural strategies and compares device metrics relevant to array-scale deployment (rectification ratio, nonlinearity, endurance, retention, variability, and operating voltage). We assess SRM-enabled in-memory computing and neuromorphic applications, as well as security functions such as physical unclonable functions and reconfigurable cryptographic primitives. Integration pathways toward CMOS compatibility are analyzed, including back-end-of-line thermal budgets, uniformity, write disturb mitigation, and reliability. Finally, we outline key challenges and opportunities: materials/architecture co-design, precision analog training, stochasticity control/exploitation, 3D stacking, and standardized benchmarking that can accelerate large-scale SRM adoption. Through the use of specialized materials and structural optimization, SRMs are set to provide selector-free, densely integrated, and energy-efficient hardware for future information processing.

**KEYWORDS** Self-rectifying memristor; Beyond-CMOS; CMOS compatibility; In-memory computing; Neuromorphic computing

Shuai Zhong, zhongshuai@gdiist.cn; Qing Wan, qing-wan@ylab.ac.cn; Yishu Zhang, zhangyishu@zju.edu.cn

<sup>1</sup> College of Integrated Circuits, Zhejiang University, Hangzhou 310027, People's Republic of China

<sup>2</sup> Yongjiang Laboratory, Ningbo 315202, People's Republic of China

<sup>3</sup> Zhejiang ICsprout Semiconductor Co., Ltd, Hangzhou 310027, People's Republic of China

<sup>4</sup> ZJU-Hangzhou Global Scientific and Technological Innovation Center, Hangzhou 310027, People's Republic of China

<sup>5</sup> Guangdong Institute of Intelligence Science and Technology, Hengqin 519031, People's Republic of China

<sup>6</sup> Department of Science, Mathematics, and Technology, Singapore University of Technology and Design, Singapore 487372, Singapore

## 1 Introduction

With the rapid advancement of information technology, Moore's law is increasingly challenged by the physical limits of device miniaturization and rising power consumption issues [1]. Although it has long driven the scaling and performance enhancement of integrated circuits [2], further miniaturization beyond the sub-nanometer regime poses significant hurdles [1, 3]. Technologies such as Fin Field-Effect Transistor (FinFET) have partially mitigated leakage currents [4], yet at the 3-nm node and below, nanosheet gate-all-around (GAA) field-effect transistors are expected to become essential [5, 6]. Moreover, the von Neumann architecture characterized by the physical separation of memory and computing units incurs substantial energy and latency penalties due to continuous data shuttling, thereby limiting overall efficiency [7]. These limitations have spurred interest in beyond-CMOS computing paradigms [8, 9], including in-memory computing and neuromorphic architectures, which merge memory and processing to eliminate data transfer bottlenecks [10, 11]. Neuromorphic computing, in particular, mimics the structure and functionality of biological neural systems, enabling highly parallel, low-power operation through deep integration of storage and computation.

The realization of ultra-large-scale neuromorphic hardware is essential for emulating brain-like functions in real time and with high energy efficiency, yet it faces critical challenges in maintaining integration density, interconnect complexity, and signal integrity. A critical enabler for such neuromorphic hardware is the passive crossbar array, which offers exceptional scalability and integration density [12, 13]. However, its practicality is hampered by sneak path currents, which impair read/write accuracy. Conventional solutions to mitigate this issue, such as the one-transistor-one-RRAM (1T1R) [14], one-selector-one-RRAM (1S1R) [15], and one-diode-one-RRAM (1D1R) [16] configurations, reduce sneak paths but incur trade-offs in complexity, footprint, power, and variability [12]. An emerging solution is the self-rectifying memristor (SRM), which incorporates inherent diode-like rectification and non-volatile memory within a two-terminal structure. This built-in nonlinearity effectively suppresses sneak currents without external components [17], streamlining design and lowering power consumption. SRMs also exhibit desirable characteristics including high nonlinearity [18, 19], tunable conductance

[20, 21], fast switching [22], and low operating power [23, 24], making them a foundational technology for advancing high-density neuromorphic computing systems. While the goal of beyond-CMOS technology is to break the performance limitations of conventional CMOS, in practice, large-scale computing arrays are realized on the premise of compatibility with existing mature CMOS processes [25–27]. This compatibility is an important factor in realizing mass production, cost reduction, and the basis for the smooth integration of new technologies into existing semiconductor manufacturing systems [28]. Therefore, beyond-CMOS technology is faced with an important contradiction to improve system performance while maintaining device compatibility with CMOS processes. Notably, SRMs compatible with CMOS processes have been extensively studied and scaled up to small-scale arrays [17, 29–31]. Meanwhile, SRMs-based in-memory computing architectures and neuromorphic computing systems have been well exploited [12, 17, 32–44], providing an ambitious blueprint for large-scale beyond-CMOS computing paradigm.

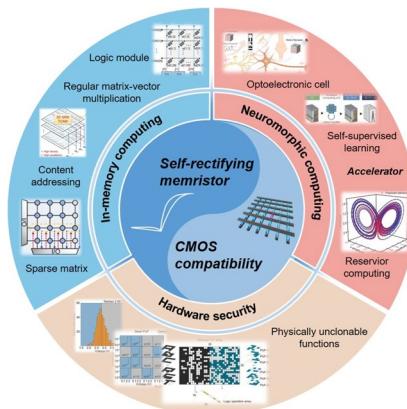

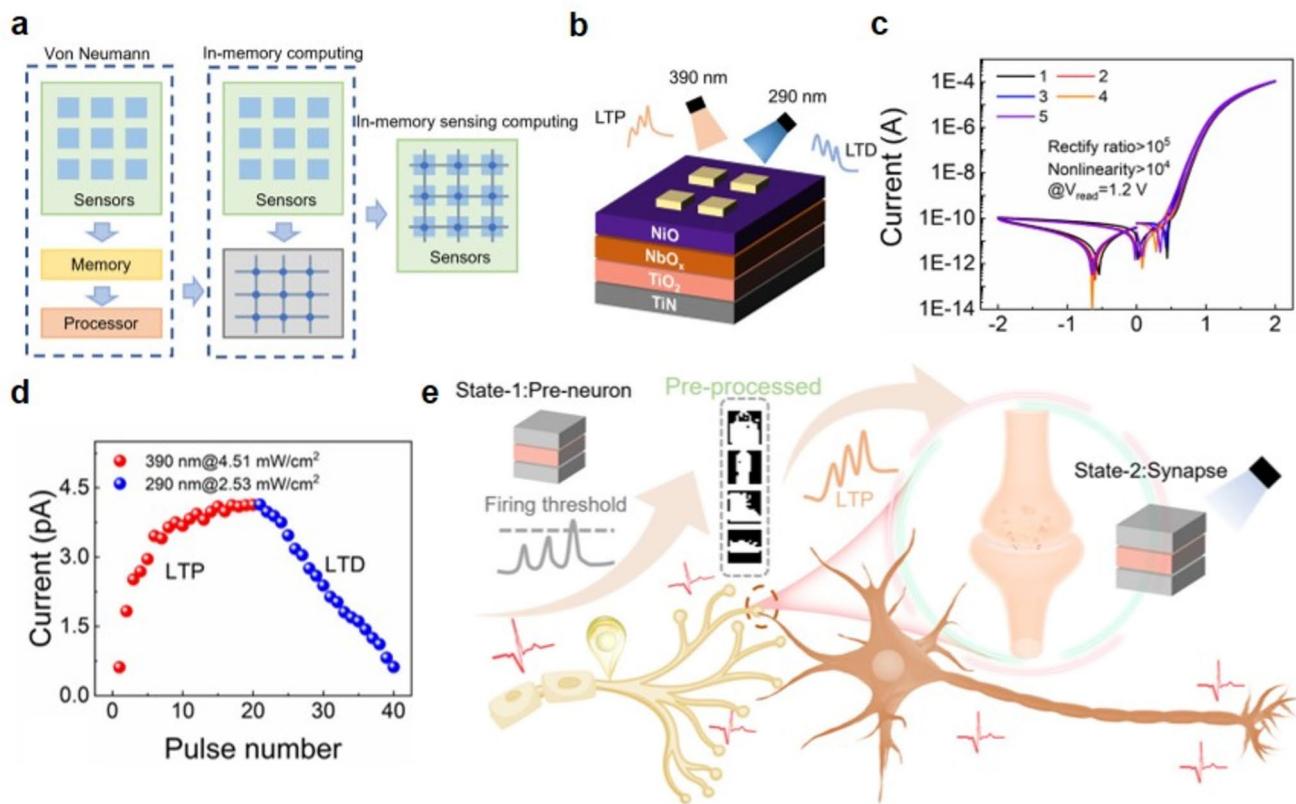

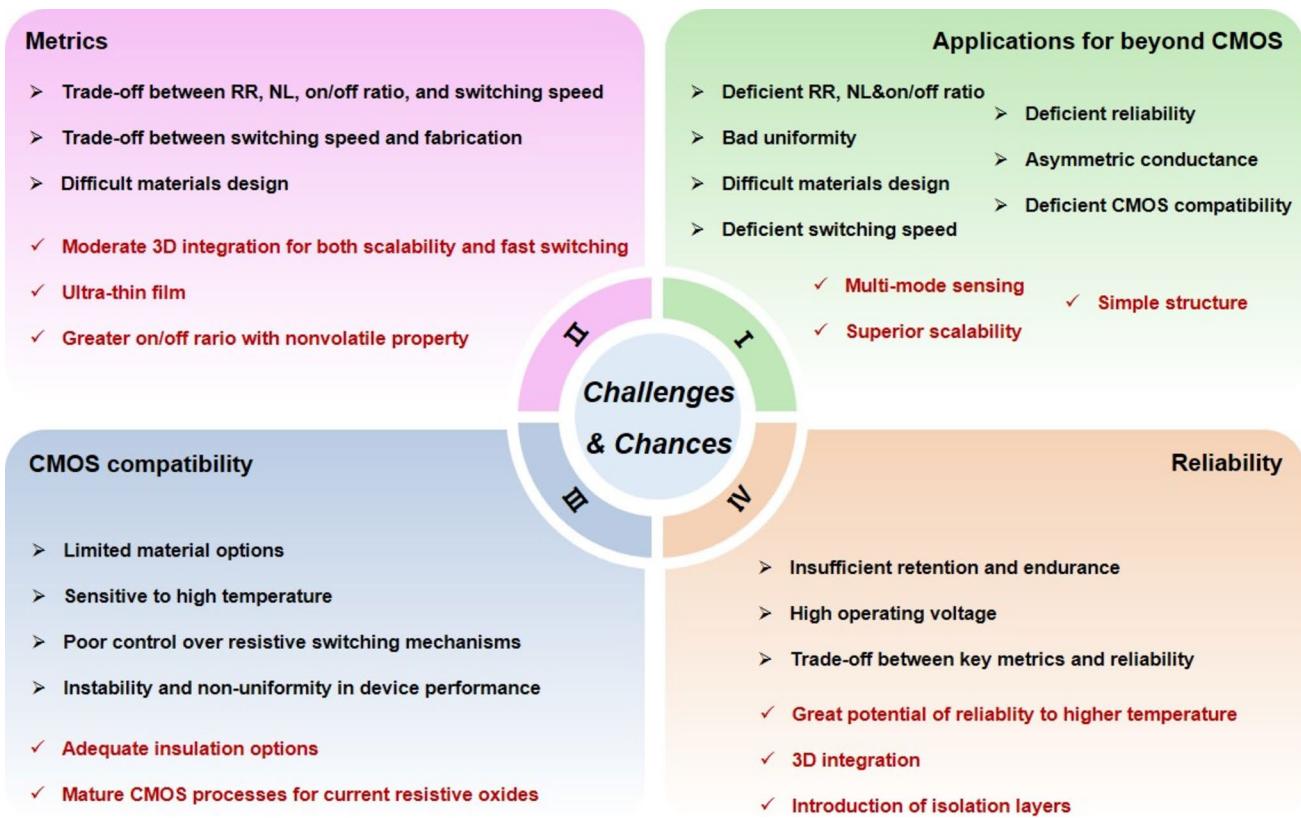

In this review, we comprehensively examine the potential of SRMs for beyond-CMOS applications, with emphasis on CMOS compatibility and implications for novel computing architectures. Through a systematic analysis of the operating mechanisms, material choices and electrical characteristics of SRMs, we evaluate their advantages and applications in in-memory computing, neuromorphic computing, and hardware security. Finally, the review discusses the prevailing challenges and future opportunities facing the development of CMOS-compatible, high-performance, low-power, and scalable computing systems (Fig. 1). All key terms used in this review and their corresponding definitions are summarized at the end of the document.

## 2 Characteristics and Mechanisms of SRM

### 2.1 Self-Rectifying Characteristics and Metrics

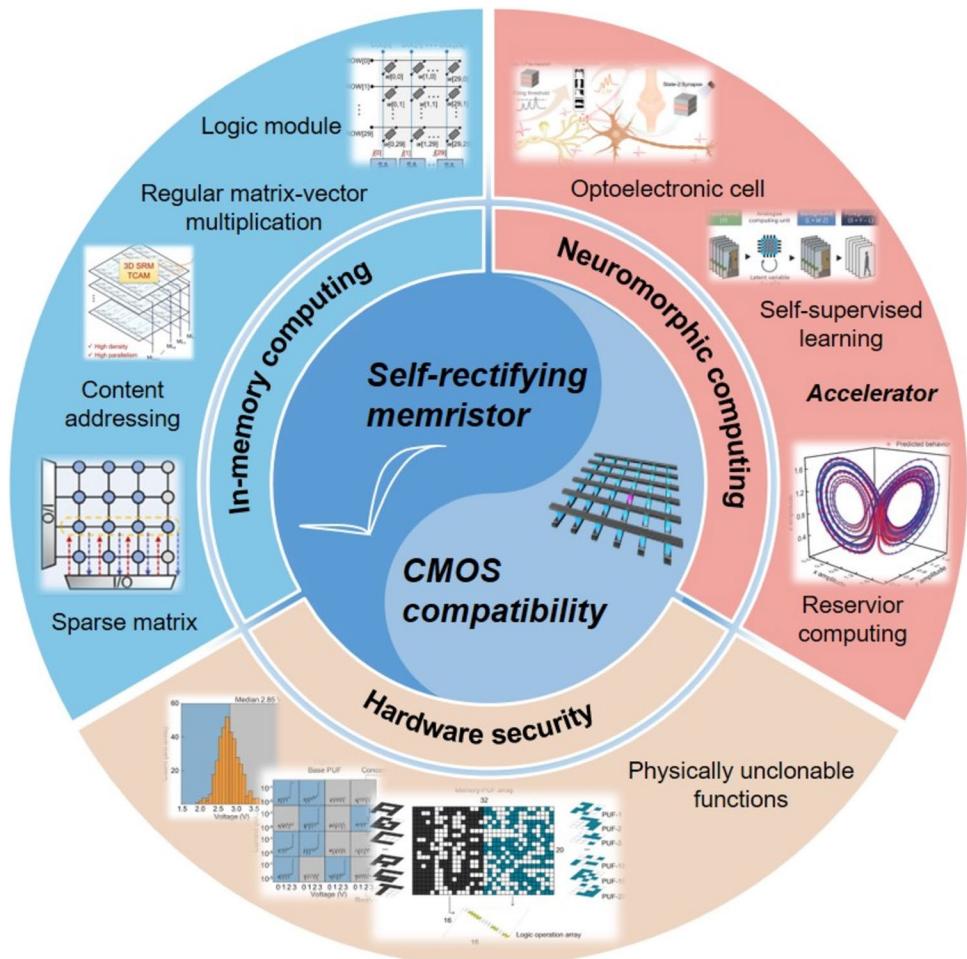

SRMs exhibit significant differences from conventional memristors in their direct-current current–voltage (DC I–V) characteristics, primarily manifested in enhanced asymmetry and nonlinearity (Fig. 2a, b). These properties stem from deliberate design of the device structure or material interface bandgaps. Conventional memristors typically exhibit symmetric or nearly symmetric

I-V loops, with relatively balanced current responses in high- and low-resistance states under positive and negative biases, respectively. This balance facilitates the emergence of “sneak paths” in crossbar arrays. In contrast, SRMs introduce mechanisms such as Schottky barriers, interfacial defect gradients, or asymmetric ion migration. This enables high conduction currents under forward bias while exhibiting strong current suppression under reverse bias, creating a pronounced rectification effect. This self-rectifying characteristic not only effectively suppresses leakage currents but also enables SRMs to achieve high-density integration without requiring external selectors (such as transistors or diodes). In this section, we will comprehensively analyze and summarize the current characteristics

and related mechanisms of SRM, and conduct a thorough discussion of its metrics.

### 2.1.1 Rectification Ratio and Nonlinearity

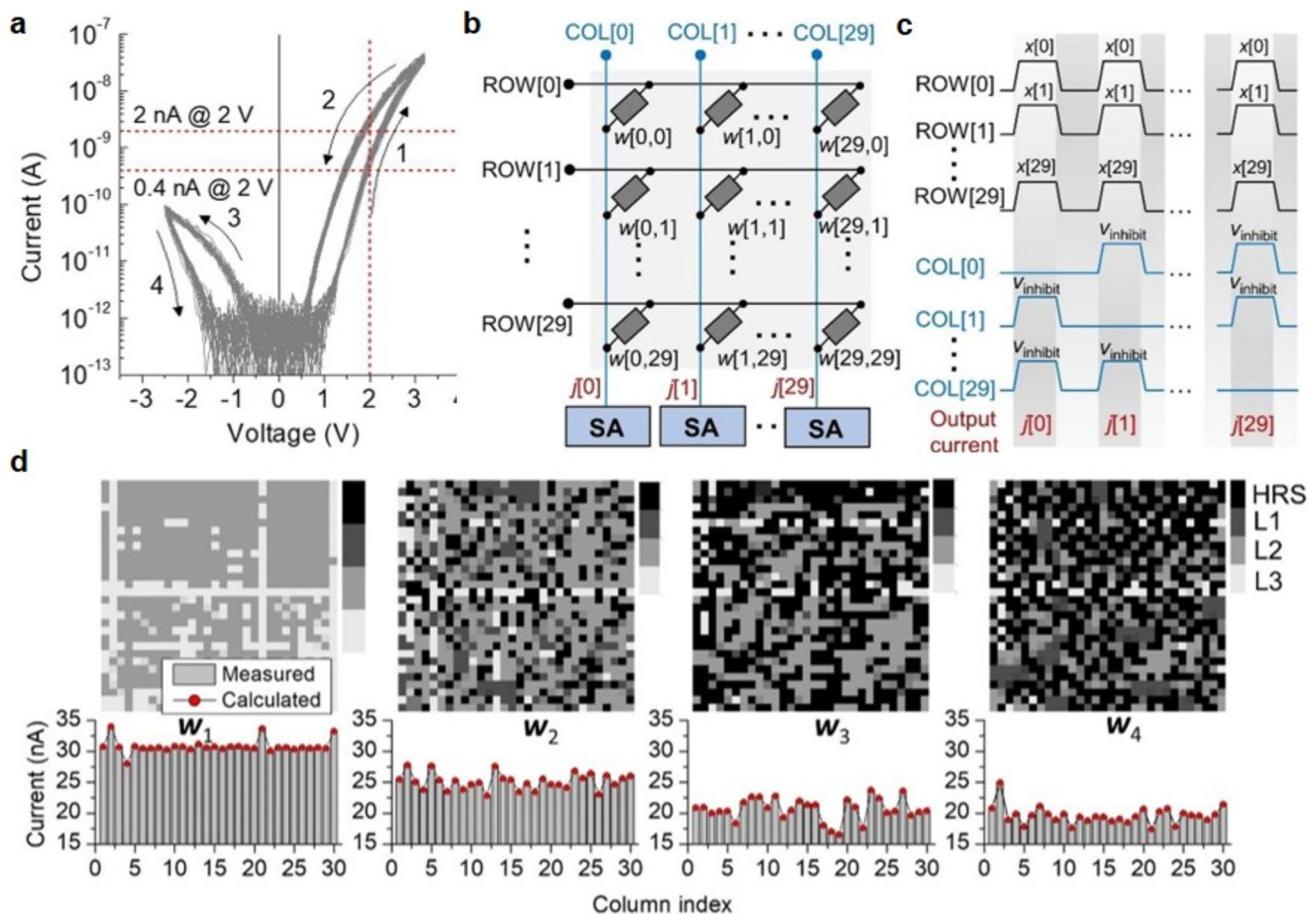

Rectification ratio (RR) is a key parameter describing the performance of SRMs and is defined as the ratio of the on-state current of the device under positive bias to the off-state current under negative bias (Fig. 2b) [17], corresponding to the unselected cells in the crossbar array (Fig. 2c) [31]. Nonlinearity (NL) is defined as the ratio of the current of the device at the read voltage under low-resistance state (LRS) to its current at the half-read voltage (Fig. 2b) with respect to the partially selected cell (Fig. 2c). Both RR and NL

**Fig. 1** SRMs have been developed for a variety of foreground beyond-CMOS applications, including in-memory computing, neuromorphic computing, and hardware security currently, where CMOS compatibility is an important basis for their further expansion. Reprinted from [17, 34, 37, 45–48], with permission from Springer Nature, American Chemical Society. Copyright 2023 American Association for the Advancement of Science

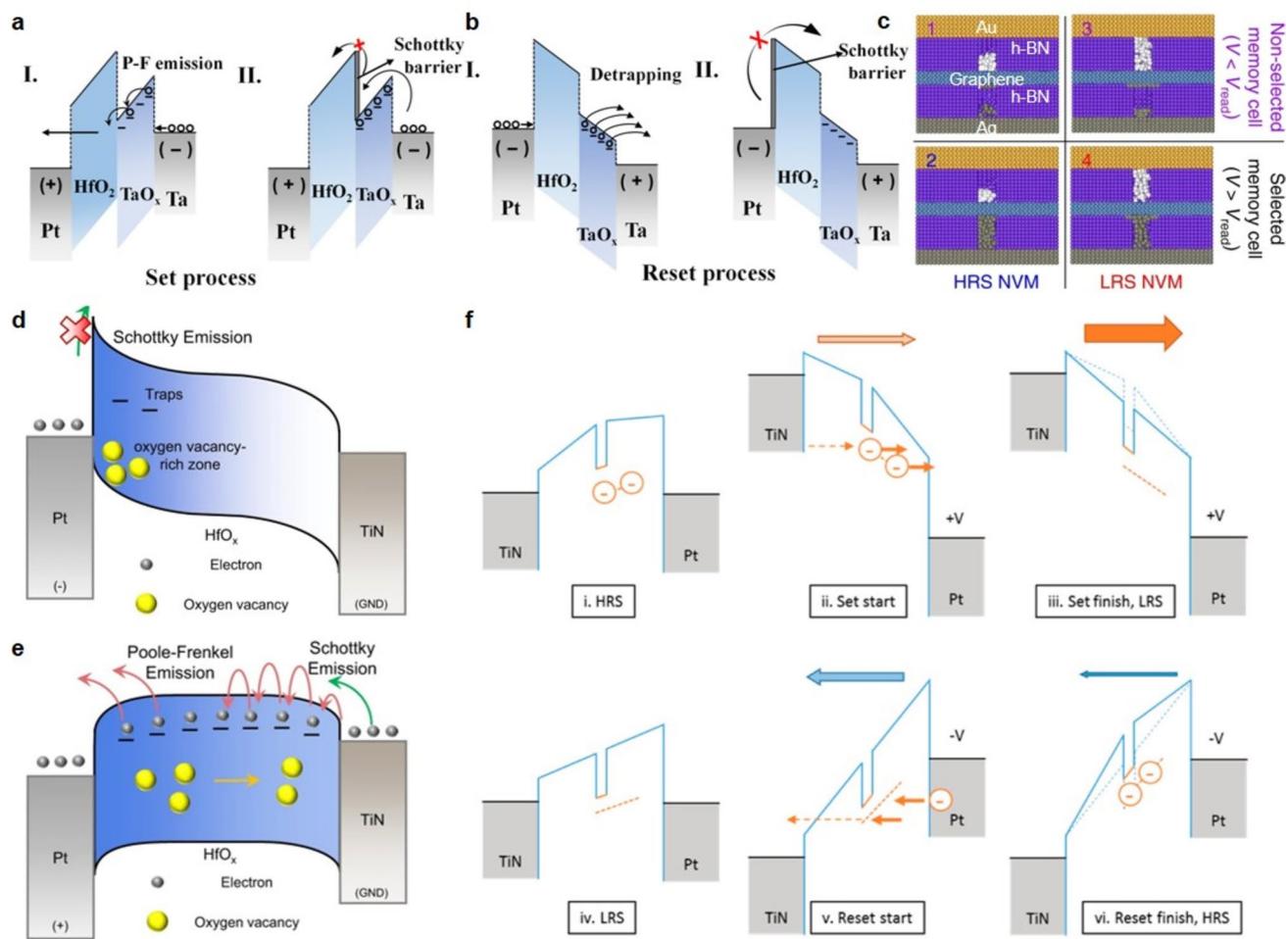

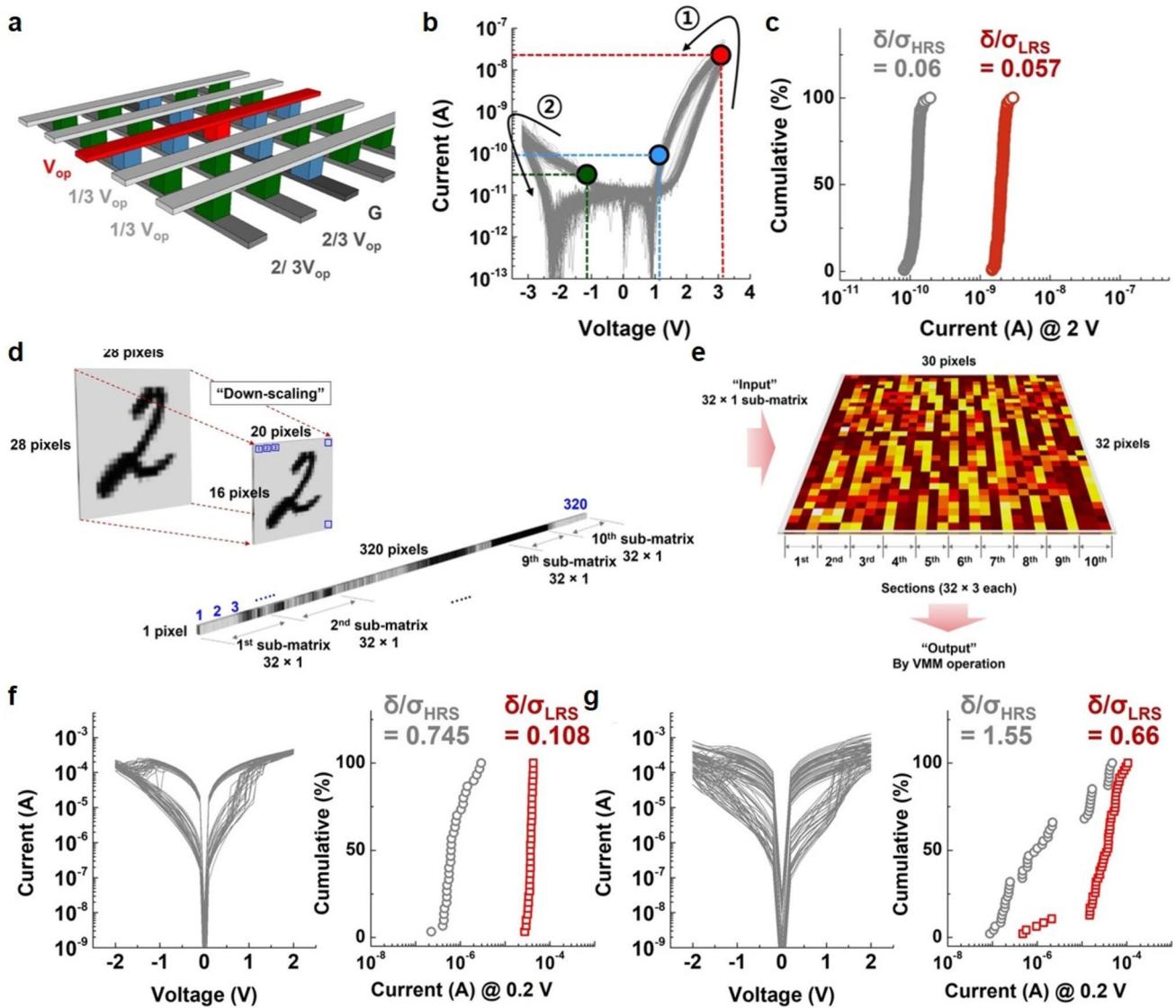

**Fig. 2** Characteristics of SRMs. **a** Typical DC I-V curves of traditional memristors. Reprinted from [32], with permission of Springer Nature. **b** DC I-V curves of the SRMs based on the structure of Pt/HfO<sub>2</sub>/TaO<sub>x</sub>/Ta. Reproduced from [17], Copyright 2023 American Association for the Advancement of Science. **c** Schematic diagram of the sneak path in the crossbar array consisting of SRMs based on Au/h-BN/Graphene/h-BN/Ag van der Waals heterojunction. Reprinted from [31], Copyright 2024 American Physical Society. The common **d** 1/2, **e** 1/3, and **f** 1/4 voltage scheme when programming SRM cells in the passive crossbar array. The blue cell denotes the selected SRM cell (ideal cell), the pink cells denote the partially selected SRM cells (nonideal cells), and the gray cells denote the unselected SRM cells (nonideal cells)

determine the level of inter-cell crosstalk in passive crossbar arrays to characterize the accuracy of write and read operations achieved by the array. They reflect the difference in current transfer capability of the device under positive and negative bias and are important parameters of the self-rectifying characteristics. They are both significantly affected by the conduction mechanism. For SRMs, the rectification characteristics mainly originate from the asymmetric structure or interface barriers inside the device. When the upper and lower electrodes of a two-terminal SRM have different figure of merit, a Schottky barrier is formed at the metal/oxide interface, and the difference in the height of this barrier leads to different electron transport characteristics under positive and negative bias. Under positive bias, the barrier decreases and the current passes easily, while under negative bias, the barrier increases and the current is suppressed. In

addition, the formation and distribution of the conducting channels affect the rectification ratio. In some SRMs, the conductive channels may be formed or enhanced only under positive bias and weakened or disappeared under negative bias to achieve the rectification behavior. For example, as described above, in ion migration-based SRMs, ions migrate to form conductive channels under positive bias, whereas under negative bias, the direction of ion migration changes, the conductive channels are weakened, and the RR and NL are thus increased significantly [12]. In short, higher RR and NL are highly desirable in SRMs as they significantly enhance array scalability and effectively suppress sneak path currents in crossbar arrays, enabling larger and more reliable passive memory and computing architectures.

### 2.1.2 On/Off Ratio

The on/off ratio of SRM refers to the current or resistance ratio of LRS to high resistance state (HRS) corresponding to its read voltage, which is usually used to measure the degree of resistance change of the memristor under different operating states (Fig. 2b) [17]. This metric is one of the key indicators of the performance of SRMs and traditional memristors, reflecting their switching ability under different resistive states as well as their read margins. The importance of the on/off ratio for SRMs is reflected in several aspects. First, a higher on/off ratio means that there is a more pronounced resistance difference between the LRS and HRS, which contributes to improved signal discrimination and stability. This is critical for applications such as storage and logic operations, as a clear distinction between resistance states reduces misreading and miswriting, thereby improving system reliability and accuracy. Second, a higher on/off ratio helps to reduce power consumption because the leakage current of the device is significantly reduced at high resistive states, which is highly compatible with the purpose of SRM. In addition, in neuromorphic computation, a high on/off ratio can better simulate the weight changes of biological synapses, thus improving the performance of neural networks. Therefore, optimizing the on/off ratio is one of the key directions to enhance the performance and scalability of SRMs and expand their applications [12, 32].

### 2.1.3 Scalability

SRM scalability is the ability to integrate SRMs into large-scale, high-density memory arrays or three-dimensional (3D) integrated architectures while maintaining their critical performance. Due to the intrinsic rectification characteristics of SRMs, the sneak path problem in the array (Fig. 2c) can be effectively suppressed, thus enabling large-scale, high-density integration from two-dimensional (2D) to 3D without adding additional selectors or transistors [14, 15, 41]. Among them, it is worth noting that compatibility with CMOS process is the basis for realizing large-scale SRM-based scaling. Commonly, in the SRM field, read margin is used to characterize the degree of scalability. Read margin is the maximum range or margin of error that can be tolerated during a read operation in a memory or logic circuit. In order to ensure the accuracy of the simulation, it is essential

to incorporate RR, NL, and on/off ratio into the calculation of the read margin (Eqs. (1) and (2)) [29]. The read margin is a critical parameter that guarantees the accurate reading of data stored in memory cells, even when the memristor crossbar array is subjected to noise or interference. A higher read margin indicates greater stability and reliability of the crossbar array during data readout, thereby preventing misreading. The one bit-line pull-up strategy is commonly used to calculate the read margin [49].

$$RM = \frac{V_{LRS} - V_{HRS}}{V_{pu}} = \frac{R_{pu}}{R_{pu} + R_{s-LRS} // R_{sneak}} - \frac{R_{pu}}{R_{pu} + R_{s-HRS} // R_{sneak}} \quad (1)$$

$$R_{sneak} = \frac{2 \times R_{1/3s}}{(N-1)} + \frac{R_{uns}}{(N-1)^2} \quad (2)$$

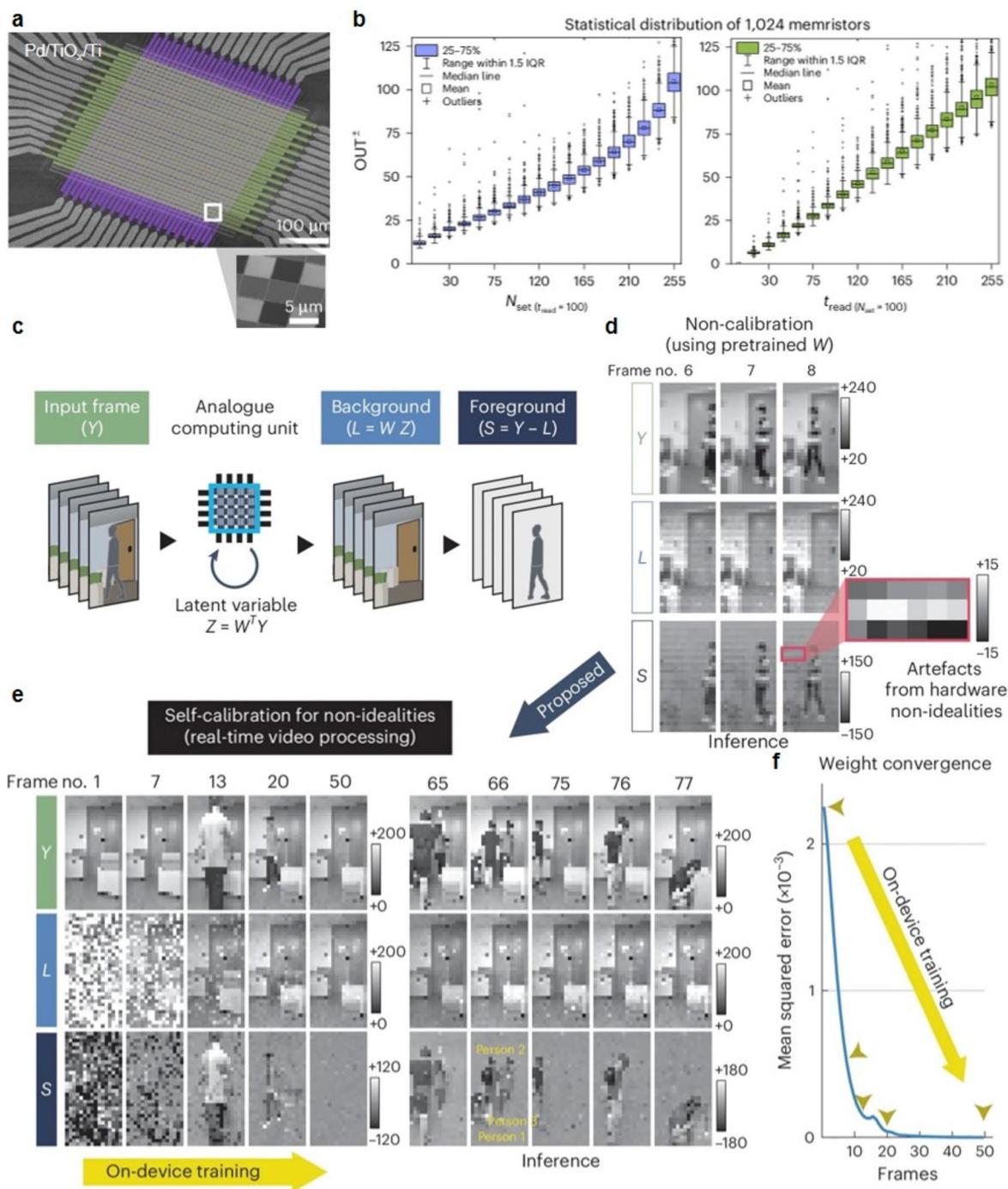

Notably, when programming SRM cells, the selection of the voltage scheme directly determines all key metrics including RR, NL, and on/off ratio, thereby impacting the scalability of the SRM and the effectiveness of sneak path suppression. Here, we first consider the 1/2 voltage scheme, as illustrated in Fig. 2d. This scheme applies the full operating voltage ( $V_{op}$ ) to the BL where the selected SRM cell resides while grounding the WL, resulting in full positive bias across the SRM cell terminals. Simultaneously, 1/2  $V_{op}$  is applied to all other WLs and BLs. In this state, partially selected cells are positively biased at 1/2  $V_{op}$ , while unselected units remain unbiased [50]. This partially mitigates crosstalk between cells in the crossbar array. Additionally, Fig. 2e, f illustrates the implementation diagrams for the 1/3 and 1/4 voltage schemes, respectively. Only when an optimal trade-off is achieved among key parameters does the selected voltage scheme become meaningful (schemes such as 1/5 or 1/6 may also be considered as appropriate [51]).

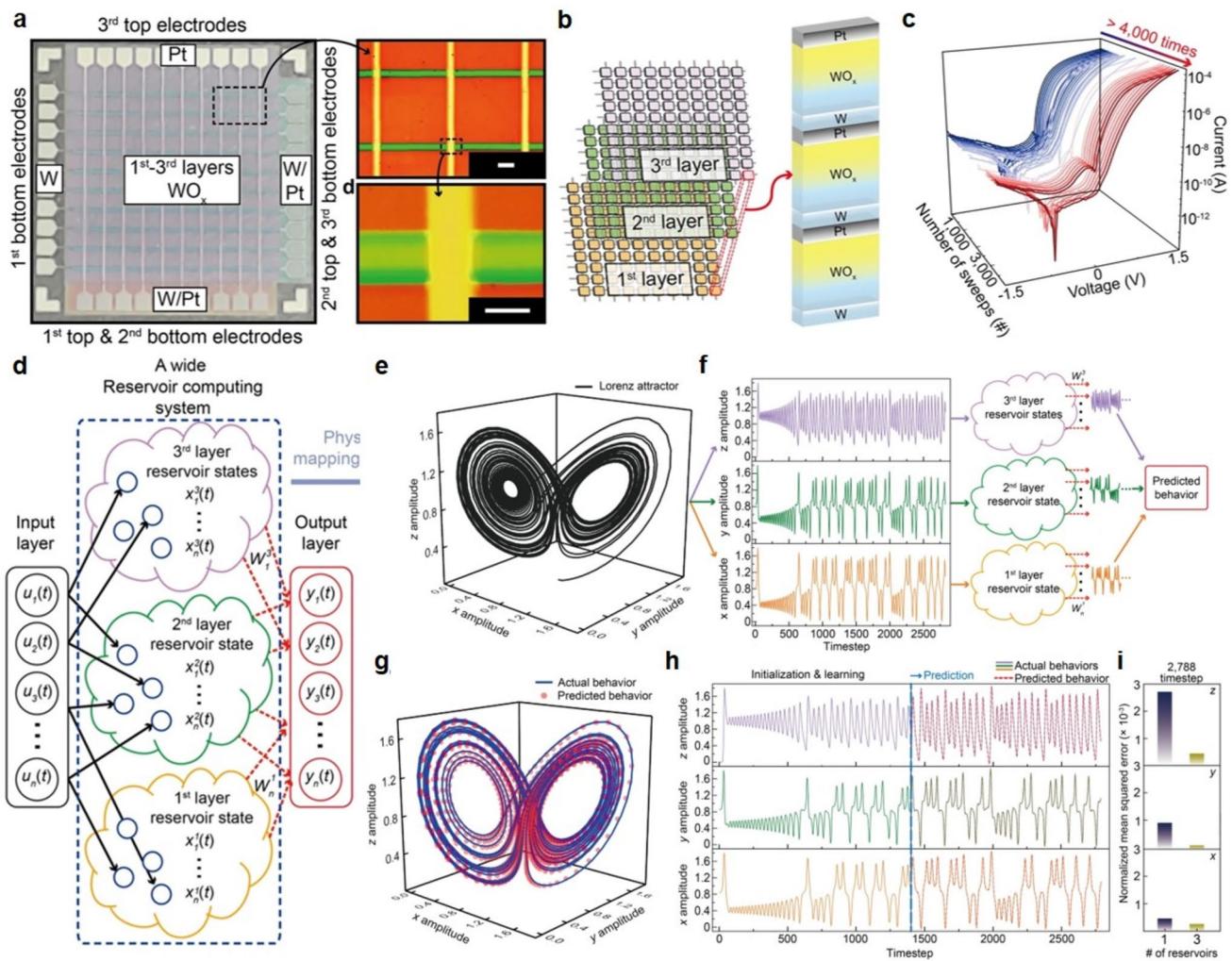

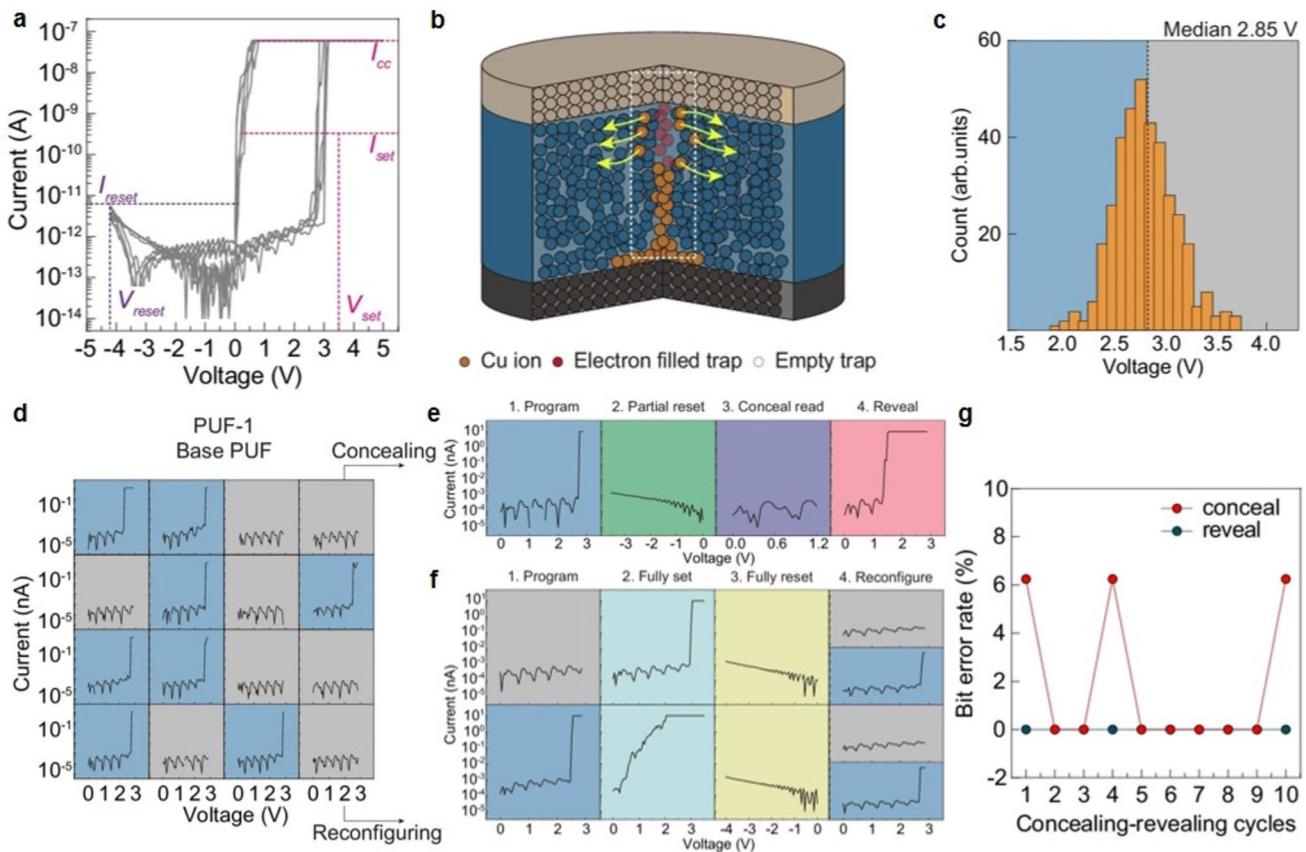

Moreover, SRM-based multilayer 3D integration technology represents the critical path to overcoming the density, energy efficiency, and crosstalk limitations of traditional compute-in-memory architectures. Its characteristics of interlayer uniformity, picosecond-level switching energy consumption, and nanosecond-level read latency provide a highly energy-efficient, high-density hardware foundation for complex tasks such as high-precision matrix solving and neuromorphic computing. Li et al. [52] successfully fabricated a 4-layer stacked, 4 Kb-capacity Ta/TaO<sub>x</sub>/HfO<sub>2</sub>/Pt 3D vertical SRM array. Through an innovative “split cell” design, they doubled the integration density and reduced bit

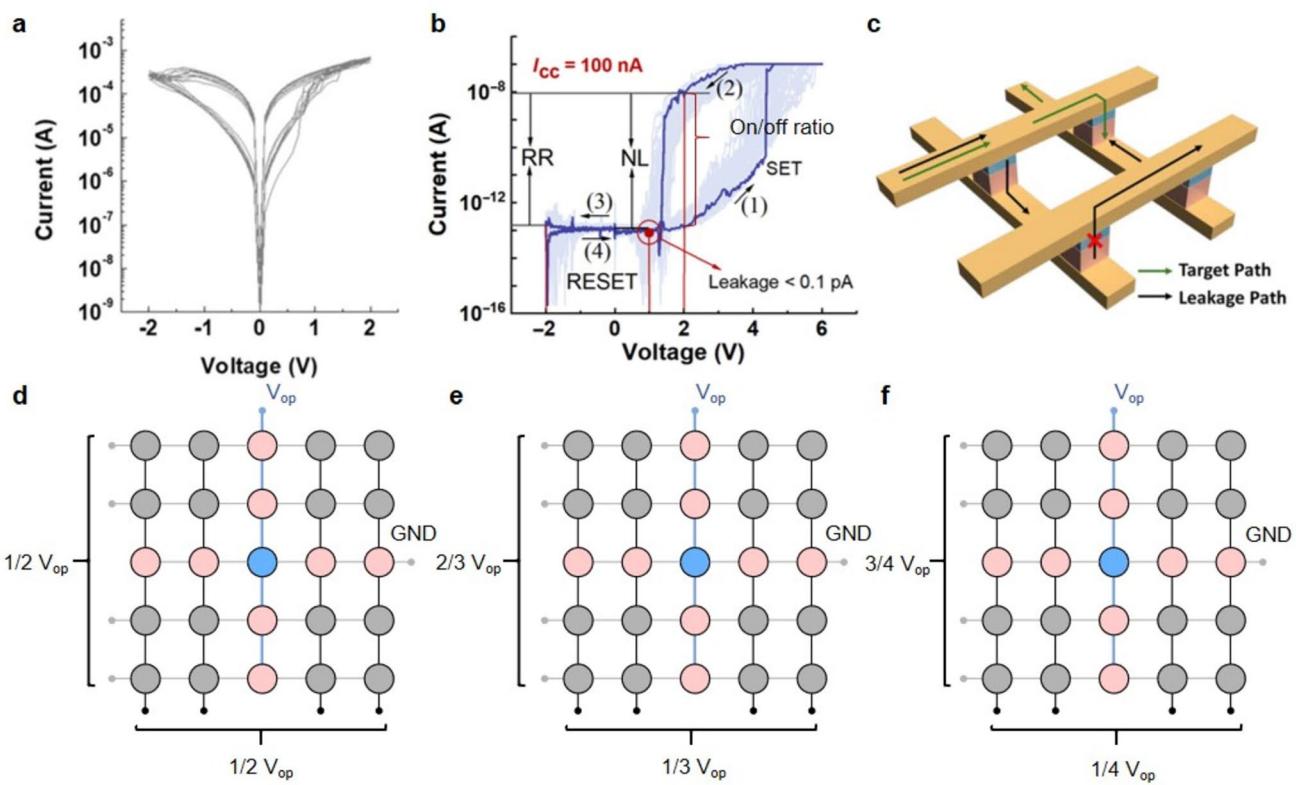

cost compared to traditional parallel cell structures. In the fabrication process, multiple pairs of  $\text{Ta}/\text{SiO}_2$  layers were alternately stacked using physical vapor deposition and plasma-enhanced chemical vapor deposition. Combined with inductively coupled plasma etching, this formed gate line structures with smooth sidewalls. Uniform  $\text{HfO}_2$  rectifying layers were prepared via atomic layer deposition, ensuring consistency and reliability in the multilayer stacking. This 3D vertical SRM exhibits excellent electrical performance with NL and RR values of approximately 6900 and 4750, respectively. Lu et al. constructed a  $\text{TiN}/\text{TiO}_x/\text{NbO}_x/\text{Ru}$  multilayer stack architecture (Fig. 3a, b) through innovative interlayer isolation and sidewall functional layer deposition techniques [49]. Without external gating devices, its ultra-high RR ( $> 10^7$ ) and NL ( $> 10^5$ ) effectively suppressed crosstalk currents, enabling 3D SRM arrays to scale beyond 1 Tb (Fig. 3c). Additionally, Ding et al. pioneered a 16-layer 3D vertical SRM [53]. By engineering band structures to form barrier peaks in  $\text{TiO}_x$  and leveraging the low oxygen vacancy aggregation tendency in  $\text{NbO}_x$ , they achieved a high NL ( $> 5000$ ).

## 2.2 Mechanisms of SRMs

The core of the SRM lies in its simultaneous capabilities of memristive switching and diode-like rectification. Memristive behavior is typically caused by the reversible formation and destruction of mobile ions (such as oxygen vacancies or metal ions), conductive filaments, or the trapping/detrapping behavior of electrons within the material [54, 55]. The transition between the HRS and LRS formed by this process

endows the device with multi-state storage capabilities. On the other hand, the rectification function relies on barrier control at the interface layer, where the barrier decreases to allow current flow under forward voltage, while under reverse voltage, the barrier significantly increases to limit current, thus creating directional conduction characteristics. Generally, the operating principle of SRMs is determined by the combined effects of material properties and structural design. In terms of material selection, functional materials with ionic migration characteristics, such as oxides and sulfides, are commonly used; in structural design, heterojunctions or asymmetry between the electrodes and the active layer form the basis for rectifying behavior. A deep understanding of this mechanism not only helps to enhance device performance but also provides an important theoretical basis for the development of new types of memory devices. Below is a detailed introduction to the mechanism including interface barrier (Schottky effect, interface oxygen vacancies), ionic migration, and trap effects (oxygen vacancies).

### 2.2.1 Interface Barrier

The core role of the interface barrier in SRMs lies in introducing asymmetric charge conduction characteristics through physical mechanisms (Schottky barrier, tunneling effect). By reasonably selecting electrode materials, regulating interface chemical properties, and utilizing the defect distribution in oxide films, the barrier height and rectification performance can be conveniently adjusted. The

**Fig. 3.** 3D integration based on SRMs. **a** Device schematic of the 3D vertical crossbar array based on  $\text{TiN}/\text{TiO}_2/\text{NbO}_x/\text{Ru}$  vertical SRM cell. **b** Optical microscope image of the stepping region from the vertical crossbar array. **c** DC I-V plot of the  $\text{TiN}/\text{TiO}_2/\text{NbO}_x/\text{Ru}$  vertical SRM cell. Reproduced from [49], Copyright 2024 American Chemical Society

rectification function of SRM is primarily caused by the different Schottky barrier heights between the two electrodes and the functional layer (Fig. 4a) [17].

Li et al. reported a p-Si/SiO<sub>2</sub>/n-Si memristor, where an asymmetric barrier exists at the Si/SiO<sub>2</sub> interface (p–n junction effect) [56]. The modulation of the electric field facilitates the formation of carrier transport paths under forward bias, while suppressing leakage current under reverse bias, thus generating self-rectifying behavior with an excellent rectification ratio ( $10^5$ ) and good retention performance ( $> 2 \times 10^5$  s). Similar to self-rectifying devices such as Pt/TiO<sub>x</sub>/Ti and Al/MoO<sub>x</sub>/Pt, Ni et al. reported a Pt/TaO<sub>x</sub>/Ta memristor, where the combination of low work function and high work function electrodes forms an asymmetric Schottky barrier, achieving directional rectification [57]. The functional layer (TaO<sub>x</sub>) acts as a switching medium, supporting HRS and LRS transitions and memory functions by regulating the internal distribution of oxygen vacancies, exhibiting superior rectification ratio and nonlinearity. Most reliable SRMs benefit from the blocking layer that restricts the disordered diffusion of charge carriers, preventing the formation of complete conductive filaments, which is a cause of leakage current. The presence of the blocking layer effectively suppresses the leakage current of the material under low voltage or reverse bias, thereby enhancing the reliability of device writing and reading. Additionally, the blocking layer can reduce power consumption, as the lower leakage current implies a more energy-efficient operating state. In numerous studies, the blocking layer forms a thin barrier, limiting the migration of ions/electrons, executing tunneling/thermionic emission mechanisms. As a result, the device's nonlinearity, durability, and data retention capability are improved. In 2023, Li et al. [17] proposed a SRM based on the Pt/HfO<sub>2</sub>/TaO<sub>x</sub>/Ta structure, where HfO<sub>2</sub> serves as the blocking layer. Under positive bias, electrons migrate through shallow energy level defects in the functional layer, with Poole–Frenkel (P–F) transport dominating the barrier crossing in the switching layer (Fig. 4a). When the positive voltage decreases to a certain value, the electron energy is insufficient to overcome this high barrier. The interruption of electron transport returns to the HRS, exhibiting high nonlinearity. Under negative voltage, a Schottky barrier forms between Pt and the blocking layer HfO<sub>2</sub>, blocking electron conduction between the electrodes and resulting in low current, leading to the rectifying effect observed in the device

(Fig. 4b). The DC I–V curves of typical SRMs are shown in Fig. 2b.

Zhang et al. reported a Pt/HfO<sub>2</sub>/WO<sub>x</sub>/TiN SRM structure, where the abundant traps in the WO<sub>x</sub> switching layer and the excellent insulating properties of HfO<sub>2</sub> synergistically promote positive polarity while suppressing negative polarity current, achieving a rectification ratio exceeding  $10^6$  [29]. Meanwhile, the increase in the thickness of the switching layer leads to a higher number of defects, resulting in a greater probability of electrons being trapped after passing through the switching layer. Under negative bias, the number of electrons emitted from traps decreases, leading to smaller leakage current. Conversely, under positive bias, more trapped electrons favor current accumulation, generating larger positive current. Lee et al. proposed a SRM based on the Ti/NiO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/Pt structure [58]. Under positive bias, the migration of oxygen vacancies from the NiO<sub>x</sub> RS layer to the Al<sub>2</sub>O<sub>3</sub> blocking layer reduces the barrier thickness in the Al<sub>2</sub>O<sub>3</sub> blocking layer, facilitating tunneling to produce high current values. Under negative voltage, the Schottky barrier at the Ti/NbO<sub>x</sub> interface and the thickening barrier of the Al<sub>2</sub>O<sub>3</sub> rectifying layer jointly suppress reverse leakage current. In 2025, Pham et al. conducted an in-depth analysis of the underlying mechanism of interfacial conduction in SRM from the perspective of band theory, making significant contributions to the advancement of this field [59]. Similarly, the HfO<sub>x</sub>/ZrO<sub>y</sub> structure also presented dominant interfacial mechanism recently [60]. These studies indicate that the self-rectifying properties are not solely determined by the material work function; the generation, distribution, and migration of ions also affect the barrier thickness and energy band height.

## 2.2.2 Ion Migration

Ion movement-type memristors utilize the migration and distribution of active ions (such as metal cations or oxygen vacancies) under an electric field to regulate the device's resistance state. Through specially designed device structures (such as gradient oxide layers), ion movement can be promoted in one direction to form conductive channels (low resistance) while being suppressed in the opposite direction (high resistance), thereby achieving the self-rectifying characteristics of the current (Fig. 4c) [41].

**Fig. 4** Mechanisms of SRMs. **a** Conductivity mechanism of double-layer oxide-based SRMs under positive bias and **b** positive bias. Reproduced from [17], Copyright 2023 American Association for the Advancement of Science. **c** Conductivity mechanism of SRMs based on Au/h-BN/graphene/h-BN/Ag van der Waals heterojunction. Reproduced from [41], with permission from Springer Nature. The conducting mechanisms, including interfacial barrier and ion migrant, of the proposed SRMs when **d** negative bias and **e** positive bias are added, respectively. Reproduced from [51], with permission of Springer Nature. **f** Illustration of the charge trapping and detrapping processes in the SRM cell based on Pt/NbO<sub>x</sub>/TiO<sub>y</sub>/NbO<sub>x</sub>/TiN structure. Reprinted from [43], Copyright 2016 American Chemical Society

Kim et al. fabricated a Pt/Na-doped TiO<sub>2</sub>/Pt-based SRM, where the asymmetric distribution of defects regulated the migration of Na ions, leading to self-rectifying behavior [36]. Lim et al. proposed alkali metal ion SRMs, utilizing lithium metal as the adhesive layer for the bottom electrode, with an alkali ion reservoir forming at the bottom of the memristor layer [61]. Aluminum dopants were used to improve retention characteristics and suppress the diffusion of alkali cations. In the optimized aluminum-doped memristor device, retention characteristics were maintained for over 20 h at 125 °C, durability exceeded  $5.5 \times 10^5$  cycles,

and high linear/symmetrical weight update characteristics were achieved.

Bae et al. developed a fluorine ion-doped TiO<sub>x</sub> SRM [42]. Fluorine ions attracted oxygen vacancies, reducing the migration energy of nearby oxygen vacancies, which improved the reversible redistribution and reduced device variability. The fluorinated memristor showed improvements in switching ratio, rectification ratio, device time uniformity, and switching speed, overcoming the trade-off between performance and reliability seen in traditional memristors. Zhang et al. reported Ni-doped WO<sub>x</sub>/ZnO SRMs, where Ni

ions reduced the electron affinity of the  $\text{WO}_x$  layer, forming asymmetric electron transport paths with shallow deep-level traps, leading to self-rectifying behavior [30]. Interestingly, the concentration gradient caused an asymmetric distribution of ions within the device, creating an internal electric field. The direction of this electric field either reinforced or weakened the applied bias direction, altering the switching bias between the on-state and off-state, resulting in nonlinear differences in conductivity under two polarities. To achieve unique dynamic functions with large-scale in-memory computing, Choi et al. fabricated dynamic  $\text{Pt}/\text{WO}_x/\text{W}$  SRMs [45]. The asymmetric distribution of oxygen vacancies in  $\text{WO}_x$  between the Pt and W electrodes led to the formation of a stable Schottky barrier at the  $\text{Pt}/\text{WO}_x$  interface and dynamic modulation of the Schottky barrier at the  $\text{WO}_x/\text{W}$  interface. The migration of oxygen vacancies driven by the electric field was observed even without externally applied compliance current, exhibiting high switching uniformity and device yield ( $> 98\%$ ), stable durability ( $> 10^5$  cycles), and low programming voltage ( $\sim 0.7$  V) for self-rectifying switching.

Wang et al. proposed an SRM structure of  $\text{Pt}/\text{WO}_3/\text{WO}_{3-x}/\text{TiN}$  [31]. The concentration of oxygen vacancies in the  $\text{WO}_x$  functional layer exhibited a gradient distribution, causing different energy level distributions at the top and bottom electrodes, resulting in asymmetric energy barriers for electron movement. This achieved a remarkable rectification ratio (approximately  $10^5$ ), a satisfactory switching ratio (approximately  $10^3$ ), low operating voltage (2 V), and high stability ( $> 10^6$  s,  $10^4$  cycles). When integrated into a  $100 \times 100$  array, the device achieved a significant resistance reading accuracy of 97.3%. Additionally, by setting the read margin at 10%, the passive array integrated with this device could reach a storage capacity of up to 180.3 Gb. Zhang et al. proposed  $\text{Pt}/\text{NiO}_x/\text{WO}_{3-x}:\text{Ti}/\text{W}$  self-rectifying devices, where the difference in work function between the rich  $\text{O}^{2-}$  region at the  $\text{NiO}_x/\text{WO}_{3-x}:\text{Ti}$  interface and the rich region of oxygen vacancies at the  $\text{WO}_{3-x}:\text{Ti}$  side formed an interface barrier, resulting in HRS and low conductivity [33]. By controlling the oxidation in the two oxide layers, the HRS current and interface barrier could be optimized, achieving ultra-high weight-enhanced linearity (0.9997). Choi et al. proposed  $\text{TaO}_y/\text{NP TaO}_x$  SRMs, where the device operation relies on the formation, movement, and aggregation of oxygen vacancies in the nanopore structure [62]. When a certain electric field is applied, the migration of oxygen vacancies changes the resistance state of  $\text{TaO}_x$  from

the HRS to the LRS, realizing memristive behavior. The self-rectifying characteristics are caused by asymmetric conduction induced by the heterojunction between the  $\text{TaO}_y$  thin film and the nanoporous  $\text{TaO}_x$  layer, achieving low-power, stable, and interference-resistant memristive switching behavior. Sun et al. [41] proposed a self-selective storage unit based on an  $\text{Au}/\text{h-BN}/\text{Graphene}/\text{h-BN}/\text{Ag}$  van der Waals heterojunction, where h-BN and graphene represent hexagonal boron nitride and graphene, respectively. Non-volatile boron vacancy layers and volatile silver layers were formed in the  $\text{Au}/\text{h-BN}/\text{Graphene}$  and  $\text{Graphene}/\text{h-BN}/\text{Ag}$  structures (Fig. 4c). In the unit integrating non-volatile and volatile structures, the graphene layer effectively prevented the diffusion of the volatile silver layer, resulting in highly nonlinear resistance switching with self-selection of  $10^{10}$  and a switching resistance ratio exceeding  $10^3$ . Further, as illustrated in Fig. 4d, e, combining interfacial barrier and ion migrant could realize surprising performance of SRMs, exemplified by the  $\text{Pt}/\text{HfO}_x/\text{TiN}$  single-layer SRM [51].

### 2.2.3 Defect Regulation

The resistive switching characteristics of devices are due to the capture and release of charge carriers (such as oxygen vacancies, metal ions, or other defect states), while the rectifying characteristics arise from controlling the filling and release directionality of charge carriers.

Kim et al. designed a low-current self-rectifying  $\text{Pt}/\text{NbO}_x/\text{TiO}_y/\text{NbO}_x/\text{TiN}$  device, where the memristive behavior is attributed to the electron capture/detrapping process, and the asymmetric barrier results in a self-rectification ratio of  $10^5$ , with trap energy levels formed up to 0.8 eV in the  $\text{TiO}_y$  layer (Fig. 4f) [43]. By optimizing the dynamic behavior of oxygen vacancies in the active layer and the design of the barrier layer, excellent performance was further achieved through using of ion migration driven by local electric fields and built-in electric fields at heterogeneous interfaces: no forming process required, self-rectification, high rectification ratio, low-power operation, and asymmetric programming voltage. Yoon et al. prepared  $\text{Ta}_2\text{O}_5/\text{HfO}_{2-x}$  based SRMs, where  $\text{Ta}_2\text{O}_5$  with high electron affinity serves as the rectifying layer [44]. Although this design weakens the Schottky barrier at the rectifying interface, it facilitates the forward injection of electrons within the dielectric layer. Cheong et al. reported a  $\text{Pt}/\text{HfO}_2/\text{Nb}_2\text{O}_5/\text{HfO}_2/\text{Ti}$  SRM,

with the  $\text{Nb}_2\text{O}_5$  layer acting as a charge trap layer [63]. Due to the oxygen scavenging effect of the bottom Ti electrode, even with the same  $\text{HfO}_2$  layer, the lower  $\text{HfO}_2$  film contains oxygen defects, which aids in trap-assisted tunneling.

Ionic memristors, relying on the dynamic migration of oxygen vacancies/ions, exhibit excellent dynamic control capabilities and multi-resistive state storage characteristics, making them suitable for online learning and neuromorphic computing, but they have poor long-term stability and complex fabrication processes. Barrier-type memristors provide high rectification ratios and stability through interface barrier engineering, making them suitable for leakage current suppression and high-density storage, but they lack dynamic control capabilities and have lower complexity, which can be optimized through multiple metal–oxide systems. Defect-type memristors, based on the distribution of material defects, offer stable switching performance and simple manufacturing processes, with lower power consumption than barrier-type memristors, making them suitable for fixed-weight storage, but their rectification ratios and dynamics are relatively limited. The choice among these three mechanisms depends on the requirements of the application scenarios.

### 2.3 Metrics

In this section, we delve into the key factors influencing the core device-level metrics of SRMs—such as RR, nonlinearity NL, CMOS compatibility, switching speed, and reliability—which have been partially introduced previously. The discussion will focus on how material selection, interface engineering, structural design, and switching mechanisms affect these critical performance parameters. By analyzing these influencing factors, we aim to provide deeper insight into the operational principles and performance limits of SRMs at the device level. A comprehensive review of array-level implementations and system applications will be presented in subsequent sections.

#### 2.3.1 Rectification Ratio

As mentioned earlier, the RR of SRMs is closely related to the energy band structure of the selected electrodes, resistive and insulating layers. For example, oxygen anion migration and barrier modulation can improve the rectification

characteristics of  $\text{TaO}_x/\text{Al}_2\text{O}_3$  memristors [64], but optimizing the thickness of the  $\text{Al}_2\text{O}_3$  switching layer requires precise control of the distribution and migration of the oxygen vacancies to achieve the expected RR. For material design, it is not the case that simply increasing the barriers of the metal–insulating layer can lead to a larger RR, but also the contact barriers of the metal–oxide at the other end as well as oxide–oxide and the state of the individual interfaces need to be considered. If the barrier between the metal–insulating layer is too large, the emitted electrons cannot tunnel through the insulating layer to the other end, thus suppressing the positive current and further not achieving a sufficient RR. In addition, the optimization requires precise control of the preparation process parameters, such as temperature, time, atmosphere, etc. When the resistive layer film needs to be prepared, it is necessary to control the temperature, time, atmosphere, etc. precisely. When the resistive layer films need to be annealed rapidly in argon or oxygen atmosphere, the increase in oxygen vacancies leads to changes in the nature of the interfacial contacts, which affects the rectification effect. Since the roughness, defect concentration, and other factors of the films at different locations are completely different, precise control of such process parameters is difficult to achieve in large-scale production, significantly increasing the difficulty of optimizing RR.

#### 2.3.2 Nonlinearity

Unlike RR, NL is mainly influenced by the first metal–oxide barrier in the conducting direction, and a proper barrier will result in a wide NL region corresponding to the SRM [17]. Optimizing NL encounters the same challenges as RR, where excessive metal–oxide and oxide–oxide barriers can similarly limit the magnitude of the peak current and thus the NL enhancement. Also, when there are too many defects such as oxygen vacancies in the resistive layer, the defects will continue to migrate and accumulate with the small electric field and thus form conductive filaments, at which point the current, which would otherwise barely increase with increasing voltage, will gradually rise, i.e., NL failure [30].

#### 2.3.3 On/Off Ratio

The on/off ratio needs to be synergistically optimized with RR and NL rather than sacrificed. First, the energy band structure

and oxygen vacancy concentration have a direct effect on the on/off ratio. For example, the increase in oxygen vacancies in the  $\text{WO}_{3-x}$  layer improves the electron trapping and de-trapping efficiencies, thus increasing the on/off ratio [31]. Subsequently, preparation process parameters such as temperature, time, and atmosphere have important effects on the energy band structure and oxygen vacancy distribution of the materials, e.g., the preparation of  $\text{WO}_3$  and  $\text{WO}_{3-x}$  layers by low-power and high-power sputtering techniques, respectively, achieves different oxygen vacancy concentrations, which in turn affect the on/off ratio [31]. Similarly, the selection of electrode materials and intermediate oxide layers has a significant effect on the on/off ratio, e.g., in the  $\text{Pt}/\text{WO}_3/\text{WO}_{3-x}/\text{TiN}$  structure, the difference in the work function between the Pt and TiN electrodes and the  $\text{WO}_3$  layer, as well as the oxygen vacancy traps in the  $\text{WO}_{3-x}$  layer, works together to achieve a high on/off ratio [31]. Wang et al. systematically verified the above phenomena and mechanisms to achieve a large on/off ratio while realizing perfect nonvolatility [31], providing a fundamental guide for large-scale scaling. However, the blind pursuit of large on/off ratios may sacrifice the data retention capability of SRMs [40], which in turn fails to store data reliably, which is unnecessary.

#### 2.3.4 Switching Speed

The optimization of the switching speed of SRMs is limited by several factors. First, SRMs usually rely on materials with nonlinear ion mobility properties, and the ion mobility rate and defect distribution of these materials directly affect the device response speed. Although few SRMs have a conductive mechanism based on conductive filaments [41], continuous conductive pathways formed by defects such as oxygen vacancies can also prevent devices from switching (conductive pathway formation is slow) [29, 31, 47]. Second, the design of the device structure has a significant impact on the switching speed; the interfacial properties between the electrodes and the memristive material, the device dimensions, and the homogeneity of the internal electric field distribution all affect the efficiency and path of ion migration, thus constraining the optimization of the switching speed. Ultra-thin oxide resistive and insulating layers enable ultrafast switching [17, 49], while increasing the thickness above 30 nm significantly slows down the switching significantly [47]. In addition, external operating conditions such as voltage amplitude, pulse frequency, and temperature can also have a significant impact on switching

speed; too high or too low a voltage can lead to material damage or impeded ion migration. Even though Lu et al. achieved ultrafast response at the ps level, the overly complex preparation process based on 16 layers limits its potential for large scaling [49]. Nevertheless, they still provided valuable instructions concerning moderate 3D integration for fast switching with ultra-thin film.

Optimizing for a higher RR or NL often involves increasing the barrier height at the device interfaces. While this can effectively suppress reverse currents, it may also increase the energy barrier for electron transport under forward bias, thereby slowing down the switching speed [65]. For example, in devices with high RR and NL, the formation and rupture of conductive filaments may require higher activation energies, leading to longer switching times.

#### 2.3.5 CMOS Compatibility

Recently, combined with  $\text{Ag}^+$ -mediated filamentary switching in the 2D perovskite channels, the design from Son et al. overcomes the voltage-consumption trade-off plaguing conventional SRMs [66]. However, constructing high-performance SRMs based on 2D materials that are incompatible with CMOS processes contradicts the path of future development. There are numerous CMOS process-compatible resistive layer oxides used for SRMs, and the one that has been extensively studied is  $\text{WO}_3$  [29–31, 45].  $\text{WO}_3$  has abundant oxygen vacancies and tunable conductive properties, and these oxygen vacancies are able to migrate under the action of an external electric field to form or break conductive filaments and achieve the resistive behavior [67, 68]. At the same time, the high thermal and chemical stability makes it perfectly compatible with CMOS processes. However, the compatibility of other mainstream resist materials with CMOS processes still needs to be further explored, for example, indium–gallium–zinc–oxide (IGZO) has excellent conductivity tunability, electron mobility, and photographic properties [69], but high temperature oxidation or annealing environments in the CMOS process can lead to the denaturation of the IGZO film. Although popular and with good CMOS compatibility, the resistive denaturation mechanism of  $\text{WO}_3$  relies on the migration of oxygen vacancies and the formation of conductive filaments, and its oxygen vacancies are poorly controllable, which therefore tends to lead to instability and poor uniformity of SRM performance.

Therefore, the development of CMOS process compatibility of other resistive oxides is a major challenge but a necessary path to achieve large-scale integration. High-k oxides, such as  $\text{HfO}_2$  [17],  $\text{Ta}_2\text{O}_5$  [44],  $\text{Al}_2\text{O}_3$  [70],  $\text{TiO}_2$  [46], and others with good CMOS compatibility, have also received much attention. For example, notably, the SRMs proposed by Zhang et al. exhibit CMOS middle-of-line compatibility, leveraging  $\text{HfO}_2$  and  $\text{TiN}$ —materials routinely integrated in intermediate fabrication stages [29], and the architecture present by Wang et al. demonstrates back-end-of-line process alignment, where Pt electrodes and  $\text{WO}_3$  layers conform to back-end metallization requirements [31]. These distinct material stacks reflect tailored integration strategies for CMOS workflows, respectively.

### 2.3.6 Reliability

The reliability characterization of SRM is consistent with that of common memristor with data retention and endurance as the two main factors [71]. As shown in Table 1, starting from 2015 until 2025, SRMs have experienced a gradual development from data retention characteristics that are generally less than  $10^4$  s to greater than  $10^4$  s or even resistant high temperature. Endurance follows a similar pattern of development. It is worth noting that reliability is very closely linked to operating voltage. High operating voltage leads to a significant increase in the electric field strength inside the SRM, accelerating the migration of oxygen vacancies or metal ions, thus promoting the formation or breakage of conductive filaments. But the ion migration under this strong electric field is often difficult to be precisely controlled, which easily triggers excessive or non-uniform filament growth and leads to unstable device performance. In addition, high operating voltages can exacerbate the Joule heating effect within the material, and the localized temperature increase may cause structural changes (e.g., crystallization or phase transitions) in the material, or even lead to chemical reactions or degradation at the interface between the electrodes and the functional layer, which further affects the endurance and data retention of the device. As a result, SRMs based on conductive filaments or continuous conductive pathways tend to be significantly less reliable than SRMs based on electromigration. However, the oxide films underlying SRMs based on electromigration to achieve high RR, NL, on/off ratio, and fast switching are as

thin as possible to 10 nm or even less than 5 nm, which may be subject to localized breakdowns and thus lead to SRM failures. Meanwhile, the continuous conductive pathways are the basis for ensuring a large on/off ratio [31, 40], creating a significant contradiction.

With RR and NL increasing, the increased barrier height may lead to more significant stress on the device materials during repeated switching cycles, potentially reducing the device's lifespan [72]. High barrier height values can also sometimes be achieved at the expense of data retention. The increased barrier heights and reduced current flow can lead to slower relaxation processes, potentially causing the device to switch back to the off-state over time. This is particularly problematic in applications requiring long-term data storage. Additionally, the higher operating voltages required to overcome these barriers can exacerbate Joule heating effects, further degrading device performance over time [12, 51]. Lowering the operating voltage to increase switching speed can reduce the stress on the device materials [73], potentially improving endurance. However, if the operating voltage is too low, it may not be sufficient to drive the necessary switching processes, leading to incomplete state transitions and reduced device reliability [74]. To balance the trade-offs of RR (or NL), speed, and endurance, one optimal approach is to further optimize the device structure and materials to achieve a moderate RR or NL while maintaining acceptable switching speed and endurance. For instance, using thin insulating layers and optimizing the doping levels can help reduce the energy barriers without significantly compromising RR and NL [42], and advanced materials with high thermal stability and low defect densities can improve endurance while maintaining high RR and NL. Moreover, using materials with high ionic mobility and optimizing the device dimensions can help achieve faster switching without significantly increasing power consumption [75, 76]. As an example, Tan et al. introduce a self-rectifying two-dimensional memtransistor, employing asymmetric metal contacts—a Schottky Platinum contact and a quasi-ohmic Bismuth contact and integrating memristor resistive switching with transistor gate tunability for advanced neuromorphic computing [77].

From the perspective of the fabrication process, the fabrication of SRMs involves several critical steps, including material deposition, annealing, and doping, each of which can significantly influence the device's performance. Understanding how specific process variations affect

**Table 1** Comparison of all key parameters of advanced SRMs

| Structure                                                                                                                                               | Year | RR                  | NL                | On/off Ratio        | Leakage Current | Operating Voltage | Speed                        | Retention                    | Endurance         | Scalability                  | Applications for beyond CMOS | CMOS Compatibility | Refs |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|-------------------|---------------------|-----------------|-------------------|------------------------------|------------------------------|-------------------|------------------------------|------------------------------|--------------------|------|

| Ta/HfO <sub>x</sub> /ZrO <sub>y</sub> /Pt                                                                                                               | 2025 | 10 <sup>4</sup>     | 7×10 <sup>3</sup> | 8×10 <sup>4</sup>   | <1 pA           | 2.5 V             | 2 μs                         | 10 <sup>4</sup> s            | 10 <sup>4</sup>   | —                            | —                            | Yes                | [60] |

| Ag/CZTSSe/Mo                                                                                                                                            | 2025 | 1.5×10 <sup>3</sup> | —                 | 1.5×10 <sup>3</sup> | >10 μA          | 0.3 V             | —                            | —                            | 150               | —                            | —                            | No                 | [80] |

| Pt/TaO <sub>x</sub> /TiN                                                                                                                                | 2025 | 10 <sup>7</sup>     | 10 <sup>7</sup>   | —                   | <1 nA           | 0.8 V             | 0.5 ms                       | —                            | —                 | —                            | Security                     | Yes                | [81] |

| Pt/HfO <sub>2</sub> /Ta <sub>2</sub> O <sub>5-x</sub> /Ti                                                                                               | 2025 | 10 <sup>4</sup>     | 10 <sup>3</sup>   | <10 pA              | 3 V             | 0.5 ms            | 10 <sup>4</sup> s            | 10 <sup>5</sup>              | 96 Kb             | Flexible                     | Yes                          | [82]               |      |

| Pt/HfO <sub>2</sub> /TiN                                                                                                                                | 2025 | 10 <sup>8</sup>     | 10 <sup>5</sup>   | <0.1 pA             | 1.5 V           | 1 ms              | —                            | 10 <sup>7</sup>              | 25.4 Tb           | ADS                          | Yes                          | [51]               |      |

| Ti/N/ANTO/TiN                                                                                                                                           | 2025 | 10 <sup>4</sup>     | 100               | <1 pA               | 1 V             | 10 ms             | 10 <sup>4</sup> s            | 3.5×10 <sup>4</sup>          | —                 | ANN                          | No                           | [83]               |      |

| Ag/P(VDF-TFE);BA                                                                                                                                        | 2025 | 10 <sup>6</sup>     | 10 <sup>6</sup>   | <10 pA              | 0.1 V           | —                 | 10 <sup>4</sup> s            | 200                          | —                 | —                            | No                           | [66]               |      |

| 2PbI <sub>4</sub> /ITO                                                                                                                                  |      |                     |                   |                     |                 |                   |                              |                              |                   |                              |                              |                    |      |

| Pt/HfO <sub>2</sub> /Ti                                                                                                                                 | 2025 | 10 <sup>5</sup>     | 10 <sup>3</sup>   | <10 pA              | 1.5 V           | —                 | 10 <sup>3</sup> s            | 100                          | 8.9 Mb            | CNN                          | Yes                          | [84]               |      |

| Pd/TiO <sub>2</sub> /Ti                                                                                                                                 | 2025 | 7×10 <sup>6</sup>   | —                 | 100                 | <1 pA           | 3 V               | 1 μs                         | —                            | 2×10 <sup>4</sup> | —                            | Self-supervised learning     | Yes                | [46] |

| Pt/WO <sub>3</sub> /WO <sub>3-x</sub> /TiN                                                                                                              | 2024 | 10 <sup>5</sup>     | 10 <sup>5</sup>   | <1 nA               | 2.5 V           | —                 | 10 <sup>6</sup> s            | 10 <sup>4</sup>              | 180.3 Gb          | ANN                          | Yes                          | [31]               |      |

| Pt/Bl <sub>2</sub> O <sub>2</sub> Se/β-Bi <sub>2</sub> SeO <sub>3</sub> /Au                                                                             | 2024 | 10 <sup>5</sup>     | 10 <sup>5</sup>   | <10 pA              | 3 V             | 20 ns             | —                            | —                            | —                 | —                            | No                           | [40]               |      |

| Pt/HfO <sub>2</sub> /WO <sub>3-x</sub> /TiN                                                                                                             | 2024 | 10 <sup>6</sup>     | 10 <sup>5</sup>   | <1 pA               | 2 V             | 0.5 ms            | 5×10 <sup>4</sup> s          | 10 <sup>6</sup>              | 21 Gb             | ANN                          | Yes                          | [29]               |      |

| Pt/ZnO/WO <sub>3-x</sub> /Ta                                                                                                                            | 2024 | 10 <sup>6</sup>     | 100               | <10 pA              | 2 V             | 1 ms              | 10 <sup>6</sup>              | 10 <sup>3</sup>              | —                 | RC                           | Yes                          | [30]               |      |

| Pt/HfO <sub>2</sub> /CuTeHO                                                                                                                             | 2024 | 10 <sup>5</sup>     | —                 | <1 pA               | 5 V             | 0.3 ms            | 10 <sup>3</sup> s (100 °C)   | 10 <sup>6</sup>              | —                 | —                            | Hardware security            | No                 | [47] |

| Au/FeO <sub>x</sub> /HfO <sub>y</sub> /Ag                                                                                                               | 2024 | 10 <sup>3</sup>     | —                 | <1 μA               | 2 V             | 50 ns             | —                            | 10 <sup>4</sup>              | —                 | CNN                          | No                           | [85]               |      |

| Ru/NbO <sub>x</sub> /TiO <sub>y</sub> /TiN (16 layers)                                                                                                  | 2024 | 10 <sup>7</sup>     | 10 <sup>5</sup>   | <10 pA              | 2 V             | 600 ps            | 10 <sup>4</sup> s            | 10 <sup>10</sup>             | 4 Tb              | ANN                          | No                           | [49]               |      |

| Pt/TiO <sub>2</sub> /NiO/ITO                                                                                                                            | 2024 | 10 <sup>3</sup>     | 10 <sup>4</sup>   | <1 nA               | 3 V             | —                 | 10 <sup>3</sup> s            | —                            | —                 | —                            | Optoelectronic ANN           | Yes                | [86] |

| TiN/TiO <sub>2</sub> /NbO <sub>x</sub> /NiO/Ru                                                                                                          | 2024 | 10 <sup>5</sup>     | 10 <sup>4</sup>   | <0.1 nA             | 2 V             | —                 | —                            | —                            | —                 | 1 Tb                         | Optoelectronic RC            | No                 | [37] |

| Au/TiO <sub>2</sub> ; Na,Al/Au                                                                                                                          | 2024 | 10 <sup>4</sup>     | —                 | 100                 | <0.1 nA         | 2 V               | 5 μs                         | 7×10 <sup>4</sup> s (125 °C) | 5×10 <sup>5</sup> | —                            | ANN                          | No                 | [61] |

| Au/Perovskite/ITO                                                                                                                                       | 2024 | 514                 | —                 | 10 <sup>3</sup>     | <10 nA          | 3 V               | —                            | 10 <sup>4</sup> s (85 °C)    | 10 <sup>4</sup>   | 3 Mb                         | —                            | No                 | [87] |

| Pt/NbO <sub>x</sub> /Ti                                                                                                                                 | 2024 | 100                 | 10                | <0.1 mA             | 4 V             | 1 ms              | —                            | 10 <sup>3</sup>              | —                 | RC                           | No                           | [88]               |      |

| Pt/Al <sub>2</sub> O <sub>3</sub> /HfO <sub>x</sub> /TiO <sub>x</sub> /Al                                                                               | 2024 | 10                  | —                 | <10 μA              | 3 V             | 1 μs              | —                            | 10 <sup>3</sup>              | 1 Kb              | RC                           | Yes                          | [89]               |      |

| Ru/Hf <sub>0.8</sub> Si <sub>0.2</sub> O <sub>2</sub> Al <sub>2</sub> O <sub>3</sub> /Hf <sub>0.5</sub> Si <sub>0.5</sub> O <sub>2</sub> TiN (2 layers) | 2024 | 10 <sup>3</sup>     | 10 <sup>2</sup>   | <10 pA              | 3 V             | 100 μs            | 10 <sup>4</sup> s (85 °C)    | 10 <sup>6</sup>              | —                 | ANN                          | Yes                          | [32]               |      |

| Au/TiO <sub>2</sub> /FTO                                                                                                                                | 2024 | 100                 | 10 <sup>3</sup>   | <10 μA              | 2 V             | —                 | —                            | —                            | —                 | —                            | Optoelectronic RC            | No                 | [90] |

| Pt/WO <sub>x</sub> /W (3 layers)                                                                                                                        | 2024 | 4.8×10 <sup>2</sup> | —                 | 4.1×10 <sup>2</sup> | <1 nA           | 1.5 V             | 0.5 ms                       | —                            | 10 <sup>5</sup>   | —                            | RC                           | Yes                | [45] |

| Pt/TiO <sub>2-x</sub> ; F/Ti                                                                                                                            | 2024 | 10 <sup>5</sup>     | —                 | 10 <sup>4</sup>     | <0.1 nA         | 3 V               | 77 ns                        | —                            | 10 <sup>6</sup>   | —                            | —                            | No                 | [42] |

| Pt/NiO <sub>x</sub> /WO <sub>3-x</sub> ; Ti/W                                                                                                           | 2023 | 10 <sup>2</sup>     | 100               | <0.1 nA             | 3 V             | 500 ms            | —                            | 500                          | —                 | SOM                          | Yes                          | [33]               |      |

| Pt/HfO <sub>2</sub> /TaO <sub>x</sub> Ta (2 layers)                                                                                                     | 2023 | 10 <sup>4</sup>     | 10                | <10 pA              | 5 V             | 200 ns            | 10 <sup>4</sup> s (85 °C)    | 10 <sup>5</sup>              | 1.56 Gb           | —                            | Yes                          | [91]               |      |

| Pt/Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> ; Al/TiN (2 layers)                                                                                 | 2023 | 10 <sup>4</sup>     | 10 <sup>4</sup>   | 10 <sup>3</sup>     | <10 pA          | 10 V              | —                            | 100 s                        | 100               | —                            | Logic                        | Yes                | [92] |

| Pt/HfO <sub>2</sub> /TaO <sub>x</sub> Ta                                                                                                                | 2023 | 10 <sup>4</sup>     | 10 <sup>4</sup>   | <0.1 pA             | 6 V             | 1 μs              | 3×10 <sup>4</sup> s (125 °C) | 10 <sup>6</sup>              | 95 Mb             | Sparse matrix multiplication | Yes                          | [17]               |      |

Table 1 (continued)

| Structure                                                                                               | Year | RR                | NL                | On/off Ratio    | Leakage Current | Operating Voltage | Speed                      | Retention                    | Endurance       | Scalability | Applications for beyond CMOS | CMOS Compatibility | Refs |

|---------------------------------------------------------------------------------------------------------|------|-------------------|-------------------|-----------------|-----------------|-------------------|----------------------------|------------------------------|-----------------|-------------|------------------------------|--------------------|------|

| Pt/Ta <sub>2</sub> O <sub>5</sub> /Nb <sub>2</sub> O <sub>5</sub> /Al <sub>2</sub> O <sub>3-y</sub> /Ti | 2023 | 5×10 <sup>4</sup> | —                 | 10 <sup>3</sup> | <0.1 nA         | 10 V              | 10 ms                      | 2×10 <sup>5</sup> s (150 °C) | 10 <sup>5</sup> | —           | ANN                          | No                 | [93] |

| Pt/Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> /TiN                                                | 2023 | 10 <sup>6</sup>   | 10 <sup>3</sup>   | —               | <1 pA           | 3.5 V             | —                          | 10 <sup>3</sup> s            | 10 <sup>6</sup> | —           | Graph analysis               | Yes                | [35] |

| TiN/TiO <sub>x</sub> /TiO <sub>x</sub> /NbO <sub>x</sub> /Ru                                            | 2023 | 10 <sup>6</sup>   | 5×10 <sup>3</sup> | —               | <1 pA           | 2.5 V             | 200 ns                     | 10 <sup>4</sup> s (125 °C)   | 10 <sup>8</sup> | 10 Gb       | —                            | No                 | [53] |

| Ru/HfZrO/TiN                                                                                            | 2022 | 100               | 100               | 10 <sup>4</sup> | <10 pA          | 3.5 V             | 1 μs                       | —                            | —               | —           | RC                           | Yes                | [94] |

| Pt/Al <sub>2</sub> O <sub>3</sub> /TaO <sub>x</sub> /Ta                                                 | 2022 | 10 <sup>4</sup>   | 10 <sup>4</sup>   | <0.1 pA         | 10 V            | 20 ms             | 10 <sup>4</sup> s (125 °C) | 10 <sup>4</sup>              | 538 Mb          | —           | Yes                          | Yes                | [70] |

| Pt/TiO <sub>2</sub> : Na/Pt                                                                             | 2022 | 10 <sup>4</sup>   | —                 | <0.1 nA         | 10 V            | 5 ms              | 10 <sup>5</sup> s          | 10 <sup>4</sup>              | —               | CNN         | No                           | [36]               |      |

| Pt/HfO <sub>2</sub> /Nb <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> /Ti                               | 2022 | 10 <sup>5</sup>   | —                 | —               | <10 pA          | 7 V               | —                          | 10 <sup>3</sup> s            | 10 <sup>4</sup> | —           | Stashing                     | No                 | [63] |

| Au/TaO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /TiN                                                | 2021 | 73                | 236               | 100             | <1 nA           | 3 V               | 80 μs                      | 2.5×10 <sup>3</sup> s        | 100             | 160 Kb      | —                            | Yes                | [64] |

| Pt/TaO <sub>x</sub> /Ta                                                                                 | 2021 | 10 <sup>5</sup>   | 10 <sup>4</sup>   | <10 pA          | 14 V            | —                 | 10 <sup>4</sup> s (85 °C)  | 10 <sup>3</sup>              | 160 Mb          | Logic       | Yes                          | Yes                | [57] |

| Au/h-BN/graphene/h-BN/Ag                                                                                | 2019 | 10 <sup>10</sup>  | —                 | 10 <sup>3</sup> | <10 fA          | 5 V               | 50 ns                      | 10 <sup>6</sup> s            | 10 <sup>6</sup> | 1 Tb        | MVM                          | No                 | [41] |

| TiN/HfO <sub>2</sub> /TaO <sub>x</sub> /Ti/TiN/W (8 layers)                                             | 2017 | 100               | 100               | <10 pA          | 6 V             | 300 ns            | 10 <sup>4</sup> s (125 °C) | 10 <sup>7</sup>              | —               | —           | —                            | Yes                | [95] |

| Pt/Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> /TiN                                                | 2016 | 2×10 <sup>3</sup> | —                 | —               | <1 pA           | 15 V              | —                          | 10 <sup>4</sup> s (125 °C)   | 10 <sup>3</sup> | —           | —                            | Yes                | [39] |

| Pt/NbO <sub>x</sub> /TiO <sub>y</sub> /NbO <sub>x</sub> /TiN                                            | 2016 | 10 <sup>5</sup>   | 10                | —               | <1 pA           | 12 V              | —                          | 3×10 <sup>3</sup> s          | 10 <sup>4</sup> | 1 Mb        | —                            | No                 | [43] |

| Ru/HfO <sub>2</sub> /TiO <sub>x</sub> /TiN                                                              | 2016 | 10 <sup>3</sup>   | —                 | <0.1 pA         | 3 V             | 400 ns            | 10 <sup>4</sup> s          | —                            | 10 <sup>7</sup> | 10 Mb       | —                            | Yes                | [96] |

| TiN/HfO <sub>2</sub> /HfO <sub>2</sub> : Si/TiN                                                         | 2016 | 300               | 10                | <1 pA           | 5 V             | —                 | 10 <sup>8</sup> s          | —                            | —               | —           | —                            | Yes                | [97] |

| Pt/Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2-x</sub> /Ti                                               | 2015 | 10 <sup>6</sup>   | —                 | 10 <sup>6</sup> | <1 pA           | 8 V               | —                          | 10 <sup>4</sup> s (200 °C)   | —               | —           | —                            | Yes                | [44] |

| TiN/HfO <sub>2</sub> /CuGeSW                                                                            | 2015 | 10 <sup>3</sup>   | 10 <sup>3</sup>   | <0.1 pA         | 4 V             | 1 μs              | 10 <sup>4</sup> s          | 10 <sup>7</sup>              | 10 Mb           | —           | —                            | No                 | [98] |

key performance metrics is also essential for developing more reliable and consistent SRM fabrication processes. First, the thickness of the active layer in SRMs is a critical parameter that affects both the RR and NL. Thicker layers generally enhance the RR and NL by increasing the energy barriers under enough forward bias [29]. Second, annealing temperature plays a crucial role in determining the crystallinity and defect density of the active layer. Higher annealing temperatures can improve the crystallinity, leading to lower defect densities and enhanced device performance [78]. However, excessively high temperatures can cause material degradation or unwanted phase transitions, negatively impacting the device's stability and performance. Last but not least, doping is a common technique used to control the electrical properties of the active layer in SRMs [42]. The concentration of dopants can significantly affect the device's on/off ratio, switching speed, and endurance. Moderate doping concentrations can increase the conductivity of the active layer, enhancing the on/off ratio and switching speed. Recently, Wang et al. epitaxially grew the AlScN film on a silicon substrate for reliable SRMs, whose crystallinity, surface roughness, and ferroelectric properties were meticulously optimized via dual-target nitrogen reactive magnetron sputtering, fine-tuning the doping ratio [79].

In summary, balancing all the metrics of SRMs while ensuring superior reliability is difficult to achieve. And current state-of-the-art SRMs are still operated at higher voltages ( $> 1.5$  V) [17, 37, 46]. Possible strategies include using multilayer stacking for fine control of the conductive pathways, optimizing the precision of the CMOS process, introducing isolation layers around the device, and protecting the device using encapsulation processes, etc. The next phase of exploration will be based on the CMOS process, the matching of the available functional materials, the high temperature reliability characterization with lower and lower operating voltage to ensure that the reliability is as synergistic as possible with the optimization of the key metrics. Besides, optimizing the performance of SRMs involves carefully balancing multiple key metrics. By understanding the trade-offs between these metrics and tailoring the device design to specific application requirements, SRMs can be optimized for high performance, reliability, and scalability in various beyond-CMOS computing paradigms. It is worth noting that all key terms mentioned in this paper are summarized and explained in Table 2.

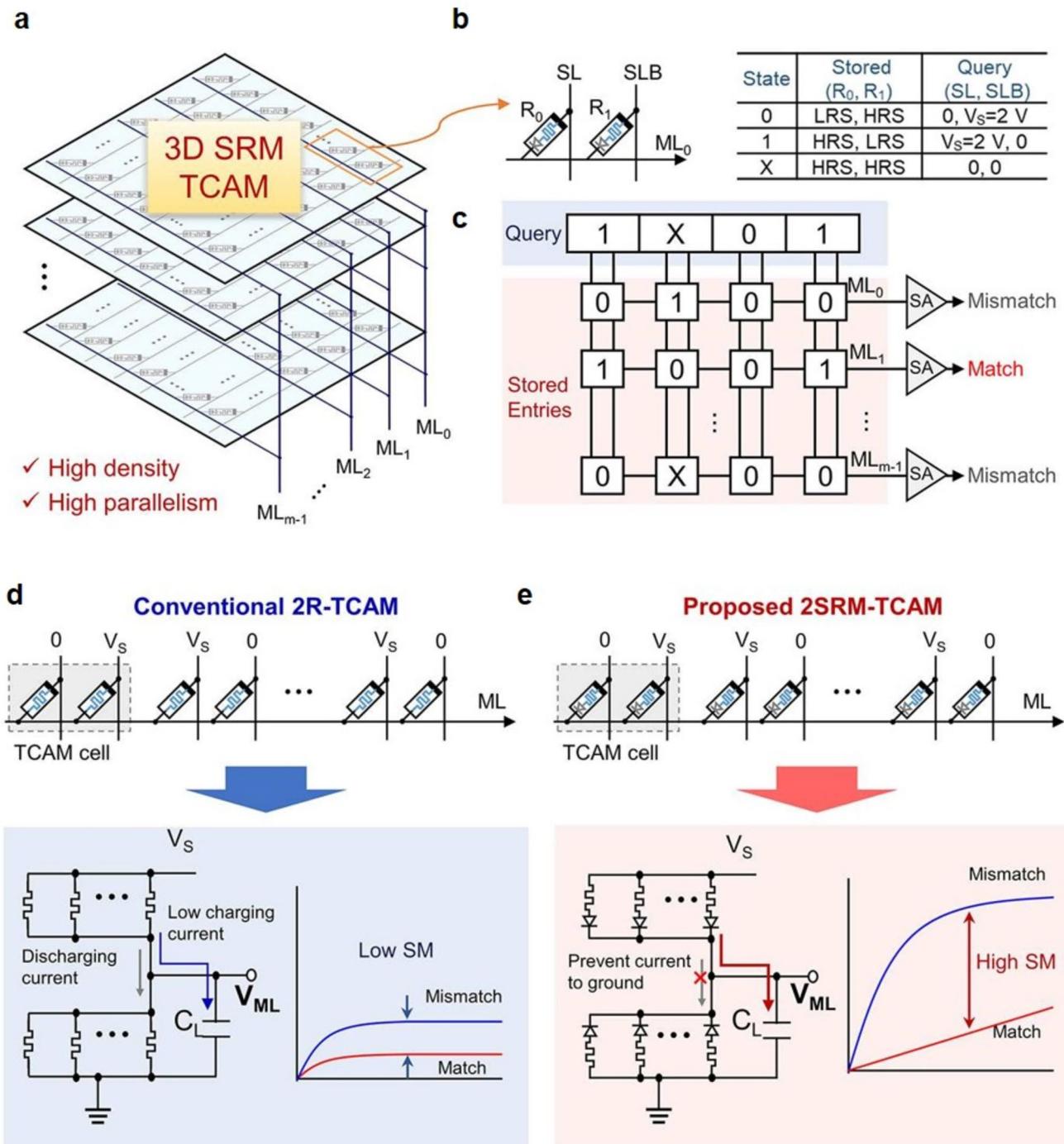

### 3 Applications of SRM in Beyond CMOS

In the previous section, we provided a detailed discussion of the working principle, conductive mechanism, and unique features of SRMs. Based on these, SRMs are capable of a large number of cutting-edge applications for beyond CMOS. The great scalability potential of SRMs provides a solid hardware foundation for ultra-high-precision in-memory computing [99], neuromorphic computing [50], and hardware security [100].

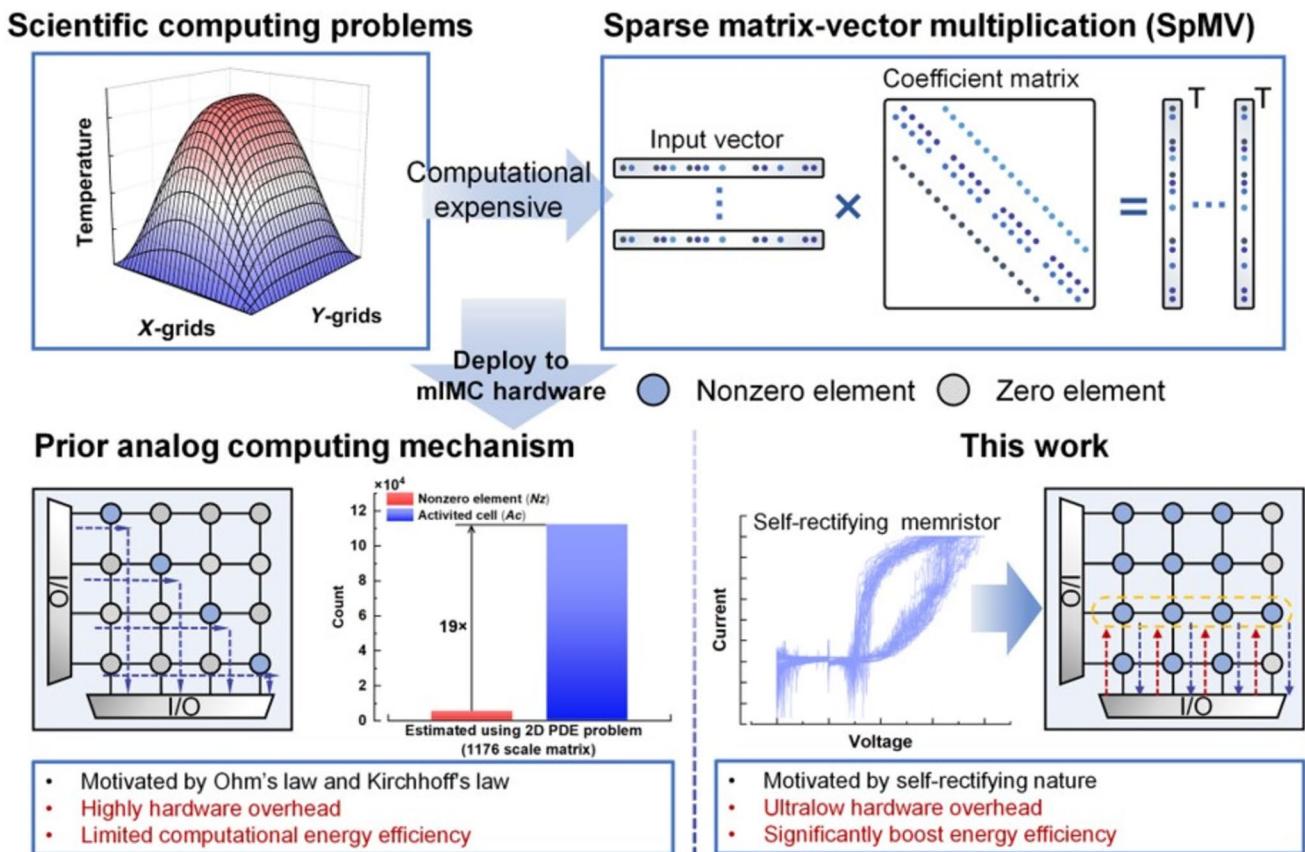

#### 3.1 In-Memory Computing

SRM-based in-memory computing utilizes the non-volatile, high-density, and programmable characteristics of memristors to efficiently perform vector matrix multiplication (VMM) by reading the rows and collecting current along the columns of memory cells, thus realizing the deep integration of memory and computing [101].

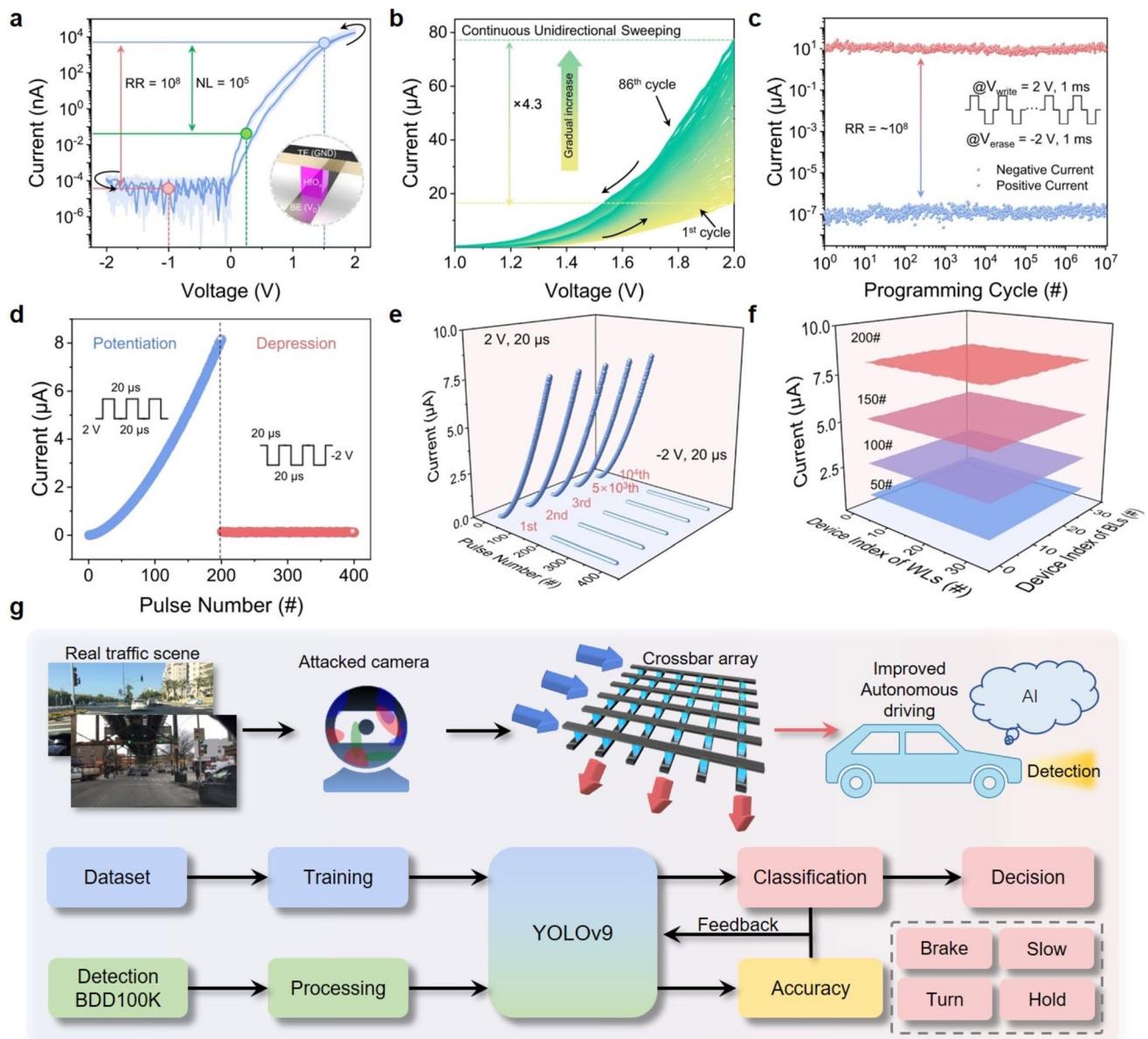

##### 3.1.1 Regular VMM

For regular VMM, the memristors are distributed as storage units at the intersection of word lines (WLs) and bit lines (BLs), and the writing and updating of the memristor resistance state can be realized by controlling the voltage of WLs, while BLs are used to read the current signals of the memristors to obtain the stored data. By storing the weights of the matrix in the conductance values of the memristors and applying the voltage signals of the input vectors on the word lines, the current of each memristor is proportional to its conductance value according to Ohm's law. The bit line collects the currents of all the memristors through Kirchhoff's law, thus directly outputting the result of the VMM [102].

As mentioned earlier, SRMs can effectively suppress leakage currents in passive crossbar arrays, thereby improving read accuracy and data accuracy. Further, the SRM cell-based crossbar arrays are able to perform multiply-accumulate computation (MAC) in a massively parallel manner. This parallelism allows the computational complexity of the VMM to be reduced from the traditional  $O(n^2)$  to  $O(n)$  or even better [103, 104], significantly improving the computational efficiency. In recent years, a large number of state-of-the-art SRMs with applications to regular VMM have

**Table 2** Key glossary

| Term                                    | Abbreviation | Definition                                                                                                                                                                                                               |

|-----------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Self-rectifying memristor               | SRM          | A novel type of memristor that exhibits intrinsic diode-like rectification, enabling unidirectional conduction and suppressing sneak path currents in crossbar arrays                                                    |

| Rectification ratio                     | RR           | The ratio of the on-state current of the device under positive bias to the off-state current under negative bias, indicating the level of current suppression in reverse bias                                            |

| Nonlinearity                            | NL           | The ratio of the current of the device at the read voltage under the low-resistance state (LRS) to its current at the partial read voltage, indicating the degree of nonlinearity in the current–voltage characteristics |

| Complementary metal–oxide–semiconductor | CMOS         | A widely used technology for manufacturing integrated circuits, characterized by low-power consumption and high scalability                                                                                              |

| Vector–matrix multiplication            | VMM          | A fundamental operation in many computing tasks, where a vector is multiplied by a matrix to produce a result vector, often used in neural networks and in-memory computing                                              |

| Ternary content-addressable memory      | TCAM         | A type of cell that allows data to be retrieved based on its content rather than its address, often used in high-speed search applications                                                                               |

| Artificial neural network               | ANN          | A computational model inspired by the structure and function of biological neural networks, used for tasks such as image recognition and pattern classification                                                          |

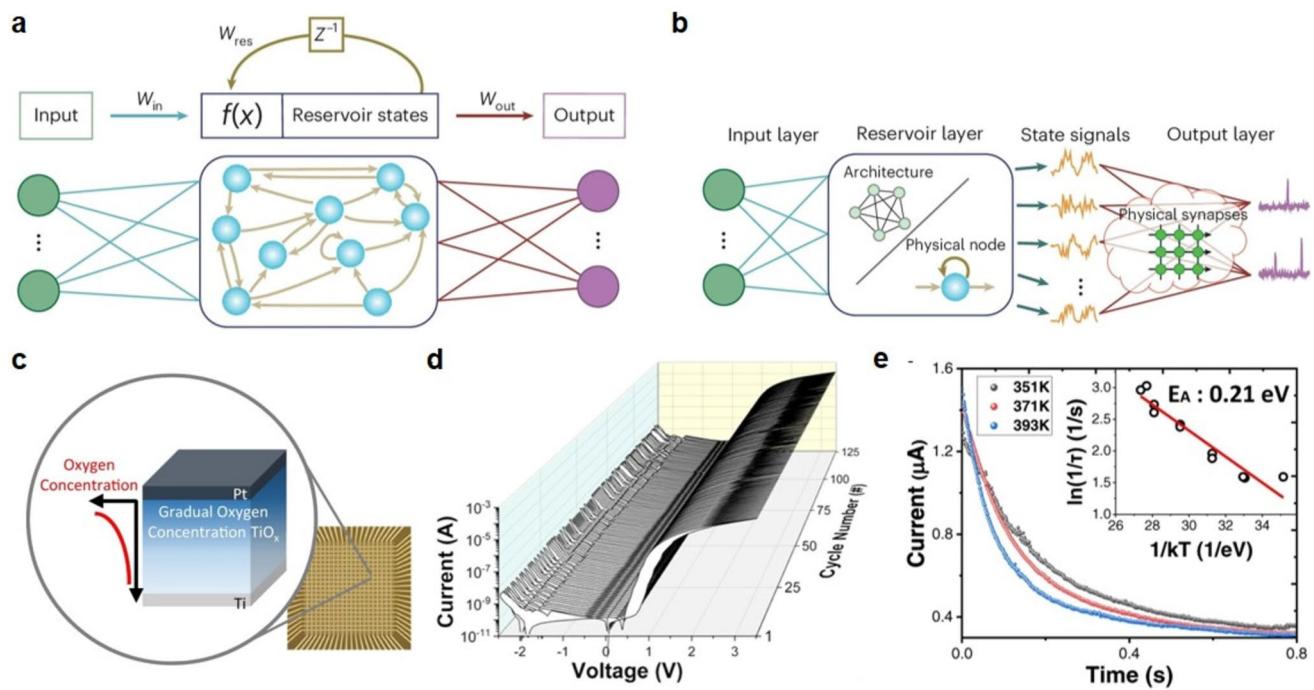

| Convolutional neural network            | CNN          | A type of neural network that uses convolutional layers to process data with grid-like topology, commonly used for image and video recognition tasks                                                                     |