# **Nano-Micro Letters**

Cite as Nano-Micro Lett. (2021) 13:164

Received: 25 May 2021 Accepted: 13 July 2021 © The Author(s) 2021

# Fully Printed High-Performance n-Type Metal Oxide Thin-Film Transistors Utilizing Coffee-Ring Effect

Kun Liang<sup>1,2</sup>, Dingwei Li<sup>1,2</sup>, Huihui Ren<sup>1,2</sup>, Momo Zhao<sup>1,3</sup>, Hong Wang<sup>3</sup>, Mengfan Ding<sup>4</sup>, Guangwei Xu<sup>4</sup>, Xiaolong Zhao<sup>4</sup>, Shibing Long<sup>4</sup>, Siyuan Zhu<sup>5</sup>, Pei Sheng<sup>5</sup>, Wenbin Li<sup>1,6</sup>, Xiao Lin<sup>7</sup>, Bowen Zhu<sup>1,6</sup>  $\bowtie$

# HIGHLIGHTS

- Fully inkjet-printed transparent high-performance thin-film transistors (TFTs) with ultrathin indium tin oxide (ITO) as semiconducting channels were achieved.

- The energy band alignment at ITO/Al2O3 channel/dielectric interface was investigated by in-depth spectroscopy analysis.

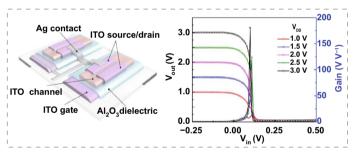

- Fully printed n-type metal-oxide-semiconductor inverters based on ITO TFTs exhibited extremely high gain of 181 at a low-supply voltage of 3 V, promising for applications in advanced electronic devices and circuits.

**ABSTRACT** Metal oxide thin-films transistors (TFTs) produced from solution-based printing techniques can lead to large-area electronics with low cost. However, the performance of current printed devices is inferior to those from vacuum-based methods due to poor film uniformity induced by the "coffeering" effect. Here, we report a novel approach to print highperformance indium tin oxide (ITO)-based TFTs and logic inverters by taking advantage of such notorious effect. ITO has high electrical conductivity and is generally used as an electrode

material. However, by reducing the film thickness down to nanometers scale, the carrier concentration of ITO can be effectively reduced to enable new applications as active channels in transistors. The ultrathin (~10-nm-thick) ITO film in the center of the coffee-ring worked as semiconducting channels, while the thick ITO ridges (>18-nm-thick) served as the contact electrodes. The fully inkjet-printed ITO TFTs exhibited a high saturation mobility of 34.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and a low subthreshold swing of 105 mV dec<sup>-1</sup>. In addition, the devices exhibited excellent electrical stability under positive bias illumination stress (PBIS,  $\Delta V_{th} = 0.31$  V) and negative bias illumination stress (NBIS,  $\Delta V_{th} = -0.29$  V) after 10,000 s voltage bias tests. More remarkably, fully printed n-type metal–oxide–semiconductor (NMOS) inverter based on ITO TFTs exhibited an extremely high gain of 181 at a low-supply voltage of 3 V, promising for advanced electronics applications.

KEYWORDS Printed electronics; Indium tin oxide; Thin-film transistors; Coffee-ring effect; NMOS inverters

Bowen Zhu, zhubowen@westlake.edu.cn

<sup>&</sup>lt;sup>1</sup> Key Laboratory of 3D Micro/Nano Fabrication and Characterization of Zhejiang Province, School of Engineering, Westlake University, Hangzhou 310024, China

<sup>&</sup>lt;sup>2</sup> Zhejiang University, Hangzhou 310027, China

<sup>&</sup>lt;sup>3</sup> Key Laboratory of Wide Band Gap Semiconductor Technology, School of Microelectronics, Xidian University, Xian 710071, China

<sup>&</sup>lt;sup>4</sup> School of Microelectronics, University of Science and Technology of China, Hefei 230026, China

<sup>&</sup>lt;sup>5</sup> Instrumentation and Service Center for Physical Sciences, Westlake University, Hangzhou 310024, China

<sup>&</sup>lt;sup>6</sup> Institute of Advanced Technology, Westlake Institute for Advanced Study, Hangzhou 310024, China

<sup>&</sup>lt;sup>7</sup> School of Science, Westlake University, Hangzhou 310024, China

# **1** Introduction

Metal oxide (MO) thin-film transistors (TFTs) have emerged as core components for large-area electronics including transparent displays, optoelectronics, and electronic skins [1–3]. Compared with their counterparts such as amorphous silicon and organic semiconductors, metal oxide semiconductors (MOS) exhibit some intriguing properties, such as high carrier mobility, wide bandgaps, and high optical transparency [4–7]. In addition, MOSs are more compatible with low-cost vacuum-free manufacturing techniques as they can achieve high device performance under relatively low processing temperature (from room temperature to 350 °C) [8–11].

To this end, solution-processed MO TFTs have been extensively studied [11-15]. The typical solution-processing technologies include screen printing, spraying coating, spin coating, and inkjet printing. In particular, inkjet printing offers advantages including direct alignment, multilayer maskless patterning, high efficiency in materials choices, fast and noncontact processing, all of which are desirable for the manufacturing of large-area low-cost electronics [16-20].

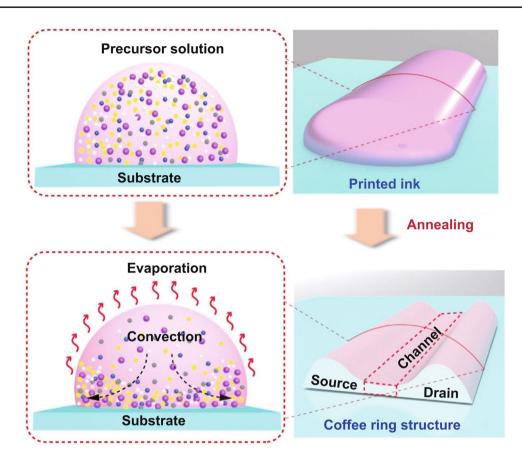

In the typical inkjet printing process, when an ink droplet dries on the substrate, the solutes tend to deposit along the periphery, resulting in concave films with thin center and thick edges. Such phenomenon is known as the "coffee-ring effect" and is conventionally unwelcoming because it not only affects film uniformity but deteriorates electrical performance [21–23]. Originated from surface tension, convective flow, and environmental conditions, coffee-ring effect is nearly inevitable in inkjet printing processes [24, 25]. To date, extensive efforts have been devoted to suppressing coffee-ring formation to achieve better film uniformity, which however, turns out to be with little success. The mobilities of most fully printed MO TFTs are relatively low (0.04–12.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) [26–29], limiting their applications in displays and circuits.

Here, on the contrary, we propose a novel printing approach that can take full advantage of such notorious "coffee-ring" effect to achieve high-performance indium tin oxide (ITO)-based TFTs and logic inverters. ITO has recently risen an excellent active channel material with high-performance mobility, beyond its conventional role as transparent conducting electrodes [30–34]. As a typical "coffeering" structure is featured with thin film in the center and

thick ridges at the edge, in our approach, we directly integrated ITO TFTs from the coffee-ring structure as-printed (Fig. 1). The ultrathin ITO film (~10 nm in thickness) in the ring center can work as excellent semiconducting channel [31–37], while the thick ITO ridges can serve as parts of source/drain (S/D) electrodes. Benefited from the ultrathin nature of the ITO channels and the integrated design, our fully inject-printed ITO TFTs demonstrated a high optical transparency (~90%) and outstanding electrical property with a high saturation mobility ( $\mu_{sat}$ ) of 34.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a low subthreshold swing (SS) of 105 mV dec<sup>-1</sup>, a near-zero turn-on voltage  $(V_{on})$  of -0.09 V, and a good current on/off ratio  $(I_{on/off})$  of ~10<sup>5</sup>. More impressively, the fully inkjetprinted NMOS inverter based on two ITO TFTs exhibited an extremely high gain of 181 at a low-supply voltage of 3 V, outperforming other documented solution-processed inverters and is even comparative to short-channel devices fabricated via vacuum-based lithography processes. Combining the merits of additive manufacturing, capability of direct patterning, and outstanding electrical performance, our fully inkjet-printed ITO TFTs hold great promise for future advanced thin-film electronics.

## **2** Experimental Section

## 2.1 Preparation of Precursor Inks and Printing Techniques

Precursor inks were prepared by dissolving corresponding metal salts in a mixed solvent of 2-methoxyethanol (2-ME), and ethylene glycol (EG) with a volume ratio of 1:1. EG was added to improve the viscosity of the inks, an important parameter to regulate the diffusion features on substrates, thus facilitating the printing processes. In addition, to optimize the electrical performance of solutionprocessed metal oxide films, we introduced two additives, acetylacetone (AcAc) and ammonium hydroxide (NH<sub>4</sub>OH), into the metal oxide precursor inks to boost the exothermic combustion reactions. In a typical printing process, indium tin oxide (ITO) precursor ink was prepared by dissolving In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O (99.999%, Sigma-Aldrich) and SnCl<sub>2</sub>·2H<sub>2</sub>O (99.99%, Sigma-Aldrich) into a mixture of 2-methoxyethanol (2-ME, Alfa Aesar, 99.3%) and ethylene glycol (Alfa Aesar, 99%) with a volume ratio of 1:1. The molar ratio of In

Fig. 1 Schematic illustration showing the formation process of the coffee-ring structure. During annealing process, the solute moved to the edges due to capillary flow, forming coffee-ring patterns

to Sn was kept at 9:1 in precursors with different concentrations (0.2 M for channel and 0.5 M for contacts). The  $Al_2O_3$ precusor solution was prepared by dissolving aluminum nitrate nonahydrate (Al(NO<sub>3</sub>)<sub>3</sub>·9H<sub>2</sub>O, Sigma-Aldrich, 99.997%) in mixed solvent of 2-ME and ethylene glycol (1:1, v:v). Then, 0.2 m acetylacetone (AcAc, Alfa Aesar, 99%) and 0.1 M ammonium hydroxide (NH<sub>4</sub>OH, 28.0% NH<sub>3</sub> in water, Alfa Aesar) were added in precursor inks solutions as additives to facilitate combustion reactions. Both ITO and  $Al_2O_3$  precursor inks were stirred at room temperature for 12 h and filtered through nylon syringe filter (0.22 µm pore size) before use.

#### 2.2 Device Fabrication and Characterization

A Dimatix (DMP-2850) printer was used to print different films with desired patterns. During printing, the substrate

temperature of the printer was set at 30 °C. ITO TFTs were printed with bottom-gate, top-contact configuration on glass substrates. The glasses were cleaned by sequential ultrasonication in acetone, isopropanol, and deionized (DI) water for 10 min before use, respectively. Subsequently, the glasses were treated with oxygen plasma for 5 min. Prior to inkjet printing of the first layer of the ITO gate electrode, a thin buffer layer of Al<sub>2</sub>O<sub>3</sub> was spin-coated on substrates at 3000 r min<sup>-1</sup> for 30 s and then annealed at 350 °C in air for 1 h, to better control the shape of the inks. In a typical printing process, 0.5 M ITO ink was firstly printed as a gate electrode with a linewidth of  $\sim 150 \ \mu m$ , and subsequently sintered at 350 °C for 1 h. Subsequently, the gate dielectric was deposited by printing 0.6 M Al<sub>2</sub>O<sub>3</sub> precursor inks onto the ITO gate contacts and baked at 200 °C for 10 min; the process was repeated three times to build up desired thickness and sufficient insulating property, and then the films were annealed at 350 °C for 1 h. Next, the ultrathin (~10 nm) ITO channel layers were printed with 0.2 M ink, above the ITO gate contacts, onto the gate dielectric layers, followed by annealing at 350 °C for 1 h. Finally, 0.5 M ITO precursor ink was printed along the ridge edges of ITO channel layers and subsequently annealed 350 °C for 1 h. All the annealing processes were conducted on a hot plate in air. After the annealing, the last printed ITO films merged with the ridge areas of preceding ITO channel layers, forming final paralleling S/D contacts. The channel width (W) and length (L) of the resulting TFTs were about 600 and 40 µm, respectively. Commercially available silver inks (Silverjet DGP 45HTG, ANP Co., LTD) were used to connect two ITO TFTs in fabricating NMOS inverters. The silver inks were annealed at 100 °C for 1 h in air after printing.

The electrical properties of the printed devices were carried out using semiconductor parameter analyzer (Keithley 4200 SCS) and/or source meter (Agilent B2912A) integrated with probe station system in ambient atmosphere in dark at room temperature. The NBIS and PIBS were performed in air at room temperature under white LED light illumination (3000 lx) with the applied gate bias of -1 and +1 V, respectively.

The values of saturation mobility  $(\mu_{sat})$  and subthreshold swing (SS) were extracted from the transfer characteristics using the gradual channel approximation model as following:

$$\mu_{\rm sat} = \frac{2L}{\rm WC_{\rm ox}} \left(\frac{\partial \sqrt{I_{\rm ds}}}{\partial V_{\rm gs}}\right)^2 \tag{1}$$

$$SS = \frac{\partial V_{gs}}{\partial (\log_{10} I_{ds})}$$

(2)

where  $I_{ds}$  denotes the drain current,  $C_{ox}$  is the capacitance of the gate dielectric, W and L are the channel width and length, and  $V_{gs}$  denotes the gate voltage. Based on the above SS value, the interfacial trap density ( $D_{it}$ ) between the semiconductor and the gate dielectric was calculated using the following equation:

$$D_{\rm it} = \left(\frac{\mathrm{SS}\log_{10}e}{kT/q} - 1\right)\frac{C_{\rm ox}}{q} \tag{3}$$

where q and T are the electron charge and measurement temperature (300 K), k is Boltzmann constant.

#### 2.3 Materials Characterization

Surface topography of printed films was measured via acmode atomic force microscopy (AFM, Cipher ES, Oxford Instruments) and surface profilometer (P-7, KLA-Tencor). AFM samples for height profile were prepared by photolithography and wet etching with diluted hydrochloric acid (1:10 in water, v:v). The chemical structure of the ITO was examined by X-ray photoelectron spectroscopy (XPS, ESCALAB XI<sup>+</sup>, Thermo Fisher Scientific) using a monochromatic Al  $K_{\alpha}$  X-ray source. XPS peaks were calibrated by taking C 1s reference at 284.6 eV. XPS depth profile analysis was performed by mild, destructive in-situ sputter etching using a 2000 eV defocused Ar<sup>+</sup> beam, and monatomic mode to achieve the required depth resolution. Transmission electron microscopy (TEM, Titan Themis 200, FEI) equipped with an energy dispersive X-ray spectrometer (EDS, super-X, Bruker,) was used to obtain the structure and chemical information on the printed oxide TFT. The crystallization and structural information of the films were obtained using X-ray diffraction (XRD, D8 Advance, Bruker) with Cu K<sub>a</sub> radiation. The optical transmittance of the printed TFTs were determined with a UV-Vis spectrophotometer (UV-3600Plus, Shimadzu) with spectrum ranging from 300 to 1200 nm.

#### **3 Results and Discussion**

#### 3.1 Printing Technique and Transistor Performance

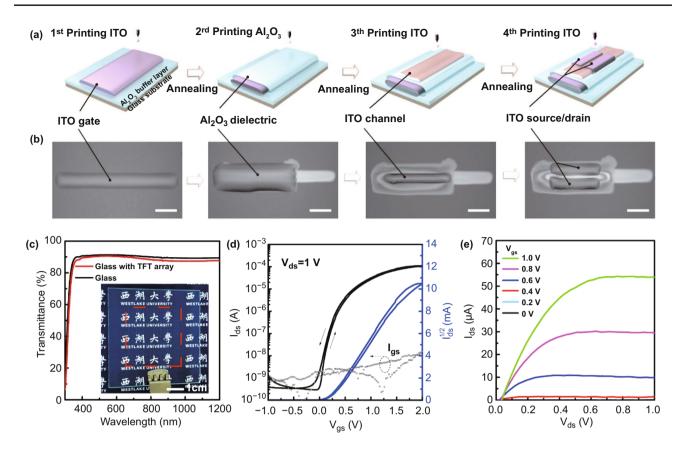

The ITO TFTs were printed with bottom-gate, top-contact configuration on glass substrates, with ITO as both channel and contact electrodes, and printed  $Al_2O_3$  as gate dielectric, as illustrated in Fig. 2a and detailed in Supporting Information. The whole printing process was conducted in ambient environment, and the corresponding optical images of each layer right after printing are presented in Fig. 2b. As shown in Fig. S1, the printed ITO film exhibited a typical coffeering structure, where the middle "valley bottom" area was thinner (~10 nm in thickness), and the edges were relatively thicker (~15 nm).

The fully inkjet-printed TFT array on glass showed high optical transparency approaching 90% in the visible spectrum, as depicted in the photo and the ultraviolet–visible

Fig. 2 Process flow of fully inkjet-printed ITO TFTs and electrical characteristics. **a** Schematic illustration of the printing processes. Each film was annealed at 350 °C for 1 h after printing. **b** Corresponding optical images of each film right after printing and before annealing. Scale bars: 200  $\mu$ m. **c** Optical transmission spectrum of fully printed TFT array on glass. Inset shows a digital photo of a glass with ITO TFT arrays. The red dashes indicate the distribution area of the printed TFT devices. **d** Transfer curves of the fully-printed TFT with ITO channel thickness of ~10 nm, and channel length/width=40/600  $\mu$ m. **e** Output characteristics of the ITO TFT with  $V_{gs}$  changed from 0 to 2 V in steps of 0.5 V, showing clear pinch-off behaviors

(UV-Vis) transmittance spectra (Fig. 2c). The dielectric properties of printed Al<sub>2</sub>O<sub>3</sub> film are shown in Fig. S2. Figure 2d, e shows the typical transfer and output characteristics of the fully inkjet-printed ITO transistors. The ITO TFT exhibited superior electrical performance of a  $\mu_{sat}$  of 34.9  $cm^2 V^{-1} s^{-1}$ , a  $V_{on}$  of -0.09 V, a low SS of 105 mV dec<sup>-1</sup>, a high  $I_{on/off}$  of 10<sup>5</sup>, low-operation voltage range of <2 V, and negligible hysteresis. To evaluate the device uniformity of fully-printed devices, the statistics of  $\mu_{sat}$ , threshold voltage  $(V_{\rm th})$ , SS, and  $I_{\rm on/off}$  of different ITO TFTs were presented (Fig. S3). These devices exhibited a mobility of  $33.1 \pm 2.4$  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  with the highest mobility of 36.0  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , a  $V_{\rm th}$  of  $0.06 \pm 0.03$  V, low SS of  $110 \pm 20$  mV dec<sup>-1</sup>, and  $I_{\rm on/off} > 10^4$ . In addition, to further study the printed devices uniformity from batch to batch and across different locations, we tested 40 devices from 2 batches at different locations. The statistical results of the  $\mu_{sat}$  and  $V_{th}$  values are shown in Fig. S4, which exhibit high uniformity with deviations <15%, indicating outstanding uniformity and reliability of the printing methods. The outstanding performance of the fully printed ITO TFTs indicated low density of impurity and defect states at the channel/dielectric interface, and the extracted interface trap density ( $D_{it}$ ) of semiconductor and gate dielectric is only  $6.5 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. In comparison, ITO TFTs fabricated on Si/SiO<sub>2</sub> substrates showed  $\mu_{sat} = 11.8$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with higher trap density ( $D_{it} = 5.3 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>) (Fig. S5).

To characterize the electrical reliability of fully printed ITO TFTs, the negative/positive bias stress (NBS/PBS) and negative/positive bias stress illumination (NBIS/PBIS) tests were performed in air without device passivation or encapsulation. The ITO TFTs were subjected to voltage bias of  $V_{\rm gs} = \pm 3$  V at room temperature. As depicted in Fig. S6, the  $V_{\rm th}$  of ITO device only exhibited minor shifts with -0.17 V at NBS and 0.24 V at PBS under stress time of 4000 s, respectively. For NBIS/PBIS, the devices were tested in ambient conditions under white light illumination (3000 lx) for a duration of 10,000 s, and a  $\Delta V_{\rm th}$  of -0.29 V (NBIS) and 0.31 V (PBIS) was observed (Fig. S7). The small  $\Delta V_{\rm th}$  shift of ITO TFTs indicates robust NBIS and PBIS stability.

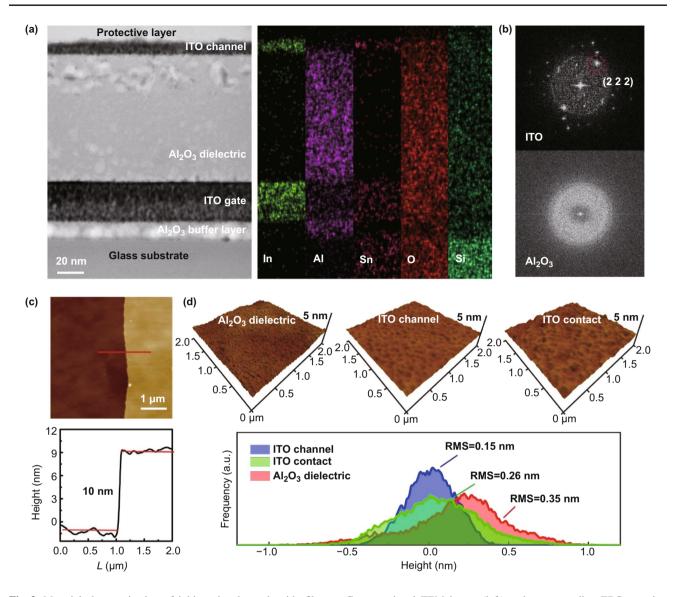

#### 3.2 Thin-Film Materials and Interface Analysis

To investigate the origin of high-performance ITO devices, we used transmission electron microscope (TEM) to characterize the structure of fully printed ITO TFTs. The crosssectional TEM image is presented in Fig. 3a, clearly showing the layered structures of Al<sub>2</sub>O<sub>3</sub> buffer layer, ITO gate, Al<sub>2</sub>O<sub>3</sub> gate dielectric, and ITO channel layers (from bottom to top). The ITO channel layer showed an ultrathin thickness of ~10 nm. The corresponding high-resolution energydispersed X-ray spectra (EDS) further confirmed the material composition and the multilayer structures of the oxide films (Fig. 3a, right). The fast Fourier transform (FFT) pattern revealed that ITO films were composed of nanocrystals with lattice spacing of 0.29 nm, corresponding to the (222) crystal plane of ITO (Fig. 3b, top), while the  $Al_2O_2$  film was amorphous (Fig. 3b, bottom). The polycrystalline and amorphous properties of ITO and Al<sub>2</sub>O<sub>3</sub> films were also confirmed by X-ray diffraction (XRD) analysis (Fig. S8). The amorphous nature of Al<sub>2</sub>O<sub>3</sub> film is beneficial for improving insulating properties and suppressing the leakage current, because the grain boundaries in polycrystalline structures provide channels for leakage current [27]. The film thickness (~10 nm) of printed ITO active channel was also confirmed by atomic force microscopy (AFM), as shown in Fig. 3c. Surface roughness is another important parameter indicating the quality of printed films. We examined the surface morphology of printed oxide films with AFM (Fig. 3d), and all the films exhibited highly flat surfaces. The root-meansquare (RMS) roughness values were only 0.35, 0.15, and 0.26 nm over  $2 \times 2 \mu m^2$  area for Al<sub>2</sub>O<sub>3</sub> dielectric, ITO channel, ITO contact films, respectively. These smooth surfaces contributed to the high mobility and stability of ITO TFTs by suppressing interface scattering and charge trapping [32].

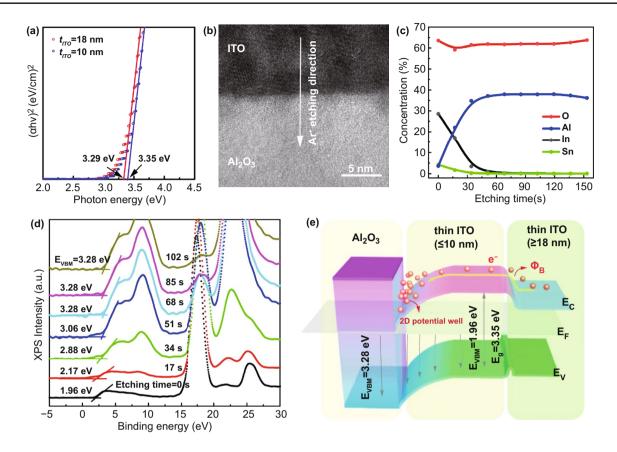

To study the energy band alignment at  $ITO/Al_2O_3$  interface, in-depth spectroscopy analysis was performed. The ITO bandgap widened from 3.29 to 3.35 eV with film thickness decreased from 18 to 10 nm (Fig. 4a), which is in good agreement with the theoretical prediction of energy quantization [38, 39]. To further reveal the influence of film thickness on carrier concentration, we performed XPS analysis on both 18- and 10-nm-thick ITO films. Figure S9 shows the O 1s XPS spectra of these films. The O 1s peak could be deconvoluted into three peaks at  $530.1 \pm 0.3$ ,  $531.6 \pm 0.2$ , and  $532.9 \pm 0.3$  eV, which were assigned to the lattice oxygen atoms (M–O) bonding, oxygen vacancies ( $V_{0}$ ), and oxygen atoms in hydroxyl groups (M-OH), respectively [40]. Oxygen vacancies were produced by defect states that acted as donor-like states, which are the major source of free carriers in metal oxide semiconductors [41]. The ratios of  $V_{0}$ were 30.5% and 42.3% for 10- and 18-nm-thick ITO films, respectively. Thicker ITO film possessed more  $V_{0}$  because the front channel is less likely exposed to the ambient oxygen during annealing, resulting in anoxic states [42]. The large proportion of  $V_{O}$  results in a higher carrier concentration, leading to reduced resistivity of the ITO films. The transfer characteristic of TFTs with different ITO channel thickness also confirmed such a transition of ITO from semiconducting to metallic behaviors (Fig. S10). As the channel thickness increases, the  $\mu_{sat}$  increases, and  $V_{th}$  shifts negatively, and the 18-nm-thick channel-based device showed very poor switching behavior. In addition, contact resistance can also affect the electrical performance of TFT. The barrier height between the channel and the source/drain electrode could strongly influence the contact resistance, and the extracted contact resistance of 18-nm-thick ITO is much lower than that of 10-nm-thick ITO by gated four-probe (GFP) method (Fig. S11). Also, the increase of gate voltage could result in the decrease of contact resistance [43].

To unveil the chemical composition and local chemical binding states of  $ITO/Al_2O_3$  heterostructure, in-situ XPS analysis with mild Ar etching was performed to obtain depth profiles. A cross-sectional TEM image showing the interface and etching direction is illustrated in Fig. 4b. As shown in Fig. 4c, the concentration of In and Sn reduced gradually (~0% after etching for 68 s), while that of Al increased instead, indicating the top ITO films were successfully etched. The corresponding XPS depth spectra of In-3*d*, Sn-3*d*, Al-2*p*, and O-1*s* with respect to varied etching time are shown in Fig. S12. Figure 4d depicts the depth-resolved valence band maximum (VBM) spectra based on the insitu XPS analysis, where distinct spectral differences can be observed. The VBM energies increased gradually from surface ITO (1.96 eV) to bulk Al<sub>2</sub>O<sub>3</sub> region (3.28 eV) with

**Fig. 3** Material characterization of inkjet-printed metal oxide films. **a** Cross-sectional TEM image (left) and corresponding EDS mapping (right) of elements indium (In), aluminum (Al), tin (Sn), oxygen (O), and silicon (Si). **b** FFT patterns obtained from the selected areas of the ITO and  $Al_2O_3$  layers. ITO exhibits nanocrystalline and  $Al_2O_3$  holds amorphous structures, and the lattice spacing of 0.29 nm corresponds to the (2 2 2) crystal plane of ITO. **c** AFM image and height profile of printed ITO channel film, showing an ultrathin thickness of ~10 nm. **d** AFM images showing the surface morphology (top) and height distributions (bottom) of  $Al_2O_3$  dielectric, ITO channel, and ITO contacts. The RMS values of ITO contact and  $Al_2O_3$  films are 0.26 and 0.35 nm, respectively. And ITO channel exhibits a narrower height distribution with RMS of only 0.15 nm

increased Ar etching time from 0 to 68 s, indicating the variation in the binding states of In approaching the ITO/Al<sub>2</sub>O<sub>3</sub> interface [44]. With etching time beyond 68 s, the VBM energies became stable at 3.28 eV, corresponding to the bulk Al<sub>2</sub>O<sub>3</sub> region. The all-energy band arrangement of ITO/ Al<sub>2</sub>O<sub>3</sub> heterostructure was illustrated in Fig. 4e. The interfacial downward band bending created a two-dimensional (2D) potential well that draws and confines free electrons supplied from the interface. This observation agrees with previous studies on heterostructures of  $In_2O_3/Al_2O_3$  [44] and  $In_2O_3/ZnO$  [38, 39]. In addition, because of the bandgap difference between thick ITO electrode and thin ITO channel layers, a barrier  $\Phi_B$  will form at the electrode/channel interface (Fig. 4e), which can suppress off current and influence threshold voltage of devices [42].

**Fig. 4** Energy band analysis of ITO/Al<sub>2</sub>O<sub>3</sub> interfaces. **a** Tauc plots of ITO films with different thicknesses of 10 and 18 nm. **b** Cross-sectional TEM image of ITO/Al<sub>2</sub>O<sub>3</sub> interface. The arrow indicates the Ar etching direction (from top ITO to bottom Al<sub>2</sub>O<sub>3</sub>). **c** Elemental concentration of In, Sn, Al, and O in the ITO/Al<sub>2</sub>O<sub>3</sub> films as a function of etching time, extracted from the XPS depth profiles. **d** Depth-resolved VBM spectra based on in-situ XPS measurements with different Ar etching time. The VBM energy increased gradually from 1.96 eV of ITO surface and became stable at 3.28 eV of bulk Al<sub>2</sub>O<sub>3</sub>. **e** Energy band diagram of the thick ITO/thin ITO/Al<sub>2</sub>O<sub>3</sub> heterostructure reconstructed based on UV–Vis and XPS depth spectra. The band bending at the ITO/Al<sub>2</sub>O<sub>3</sub> interfaces induced a 2D potential well confining free electrons. And a barrier  $\Phi_B$  exists at ITO channel and electrode layers due to the difference in bandgap

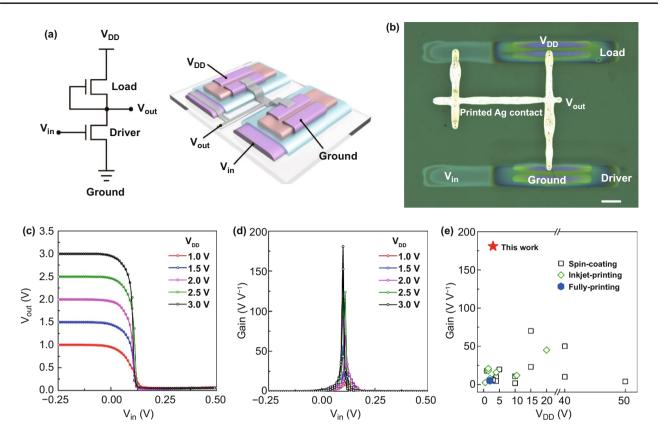

#### 3.3 Fully Printed High-Gain NMOS Inverter

To explore the potential applications of fully printed ITO TFTs, we integrated a NMOS inverter using two ITO transistors printed on glass substrate. The circuit diagram and device structure are illustrated in Fig. 5a. Printed silver electrodes were used to bridge the contacts of two ITO TFTs. An optical image of the inverter is presented in Fig. 5b, the top TFT (load TFT) worked as a depletion load to limit the current flowing through the bottom TFT (driver TFT). Figure 5c shows the voltage transfer characteristics of the printed inverter at different supply voltages. When the input voltage ( $V_{in}$ ) was lower than the threshold voltage (logic "0"), the output voltage ( $V_{out}$ ) was equal to  $V_{DD}$  (logic "1"). With  $V_{in}$  exceeding the threshold voltage (logic "1"), the

$V_{out}$  decreased abruptly to ~0 V (logic "0"), indicating the driver TFT was in a nearly short-circuit state due to the high mobility and large on-state current of ITO TFT. This implies that the load and driver TFTs showed excellent on-state and off-state behaviors in the inverter. Remarkably, the NMOS inverter exhibited the maximum transfer gain of 181 at a low-supply voltage of  $V_{DD}=3$  V, and still a high gain of 96 at a lower  $V_{DD}=2$  V (Fig. 5d), by virtue of the high mobility, small SS, and low off-state current of the fully printed ITO TFTs. Our inverter outperformed other solution-processed metal oxide TFTs reported previously (Fig. 5e). A detailed comparison among inverters based on different solution-processing techniques is presented in Table S1. The fully inkjet-printed high-gain inverter opens new opportunities

**Fig. 5** Fully inkjet-printed NMOS logic inverter based on ITO TFTs. **a** Circuit diagram and schematic illustration of the NMOS inverter structure. **b** An optical image of logic inverter based on two ITO TFTs connected by inkjet-printed silver contacts. Scale bar: 200  $\mu$ m. **c** Input–output ( $V_{in}-V_{out}$ ) voltage characteristics of the inverter under various supply voltages. **d** Corresponding gains of the NMOS inverter, showing a maximum gain of 181 at  $V_{DD}=3$  V. **e** Benchmark of inverter performance as a function of supply voltage for inverters based on metal oxide semiconductor TFTs with different solution-processing techniques and the fully inkjet-printed ITO TFTs in this work. The data were taken from Table S1

for boosting inkjet printing techniques in delivering highperformance low-power circuits.

# **4** Conclusions

In conclusion, we report fully inkjet-printed high-performance electronics by integrating the coffee-ring structured ITO generated during the printing process. In such ITO TFTs, the ultrathin ITO film (~10 nm in thickness) in the center showed widened bandgap and reduced oxygen vacancies, which could serve as excellent semiconducting channels. The thick ITO ridges, on the other hand, served as the parts of source/drain (S/D) electrodes. The fully printed ITO TFTs exhibited high transparency (90% in visible spectrum), low-operation voltage (<3 V), high mobility (34.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), and low subthreshold swing (105 mV dec-1). The fully printed ITO TFTs exhibited outstanding electrical stability with small  $\Delta V_{\text{th}}$  values of -0.17, 0.24, -0.29, and 0.31 V for NBS, PBS, NBIS, and PBIS tests, respectively. Also, the printed devices exhibited outstanding uniformity and reliability. More impressively, our fully printed NMOS inverter exhibited an extremely high gain (181) at a low-supply voltage (V<sub>DD</sub>=3 V), outperforming other solution-processed metal oxide counterparts, and was comparative to the devices fabricated from vacuum processes. Our work bridged the gap between high-performance TFTs and the solutionbased printing technologies, holding great potential for the further application in large-area, low-cost electronic devices and circuits. Acknowledgements This research was financially supported under the Westlake Multidisciplinary Research Initiative Center (MRIC) Seed Fund (Grant No. MRIC20200101). This work was performed in part at the Westlake Center for Micro/Nano Fabrication and the Instrumentation and Service Center for Physical Sciences (ISCPS), Westlake University. B.Z. thanks Prof. Yang Yang, UCLA, for discussion and suggestions. The authors acknowledge Dr. Taofei Zhou, Dr. Xiaohe Miao, and Dr. Lin Liu of ISCPS, and Mr. Danyang Zhu of Westlake University for technical assistance.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

**Supplementary Information** The online version contains supplementary material available at https://doi.org/10.1007/s40820-021-00694-4.

# References

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano et al., Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432(7016), 488–492 (2004). https://doi.org/10.1038/natur e03090

- S. Lee, A. Nathan, Subthreshold Schottky-barrier thin-film transistors with ultralow power and high intrinsic gain. Science 354(6310), 302–304 (2016). https://doi.org/10.1126/ science.aah5035

- N. Nakatsuka, K.-A. Yang, J.M. Abendroth, K. Cheung, X. Xu et al., Aptamer–field-effect transistors overcome Debye length limitations for small-molecule sensing. Science 362(6412), 319–324 (2018). https://doi.org/10.1126/science.aao6750

- M. Sugiyama, T. Uemura, M. Kondo, M. Akiyama, N. Namba et al., An ultraflexible organic differential amplifier for recording electrocardiograms. Nat. Electron. 2(8), 351–360 (2019). https://doi.org/10.1038/s41928-019-0283-5

- L. Petti, N. Münzenrieder, C. Vogt, H. Faber, L. Büthe et al., Metal oxide semiconductor thin-film transistors for flexible electronics. Appl. Phys. Rev. 3(2), 021303 (2016). https://doi. org/10.1063/1.4953034

- 6. Y.S. Rim, H. Chen, B. Zhu, S.H. Bae, S. Zhu et al., Interface engineering of metal oxide semiconductors for biosensing

applications. Adv. Mater. Interfaces **4**(10), 1700020 (2017). https://doi.org/10.1002/admi.201700020

- X. Yu, T.J. Marks, A. Facchetti, Metal oxides for optoelectronic applications. Nat. Mater. 15(4), 383–396 (2016). https:// doi.org/10.1038/nmat4599

- E. Fortunato, P. Barquinha, R. Martins, Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24(22), 2945–2986 (2012). https://doi.org/10.1002/adma. 201103228

- Y.-H. Kim, J.-S. Heo, T.-H. Kim, S. Park, M.-H. Yoon et al., Flexible metal-oxide devices made by room-temperature photochemical activation of sol-gel films. Nature 489(7414), 128–132 (2012). https://doi.org/10.1038/nature11434

- S. Choi, S.I. Han, D. Kim, T. Hyeon, D.-H. Kim, High-performance stretchable conductive nanocomposites: materials, processes, and device applications. Chem. Soc. Rev. 48(6), 1566–1595 (2019). https://doi.org/10.1039/C8CS00706C

- M. Coll, J. Fontcuberta, M. Althammer, M. Bibes, H. Boschker et al., Towards oxide electronics: a roadmap. Appl. Surf. Sci. 482, 1–93 (2019). https://doi.org/10.1016/j. apsusc.2019.03.312

- R. Chen, L. Lan, Solution-processed metal-oxide thin-film transistors: a review of recent developments. Nanotechnology 30(31), 312001 (2019). https://doi.org/10.1088/1361-6528/ab1860

- M.-G. Kim, M.G. Kanatzidis, A. Facchetti, T.J. Marks, Lowtemperature fabrication of high-performance metal oxide thin-film electronics via combustion processing. Nat. Mater. 10(5), 382–388 (2011). https://doi.org/10.1038/nmat3011

- Y.S. Rim, H. Chen, Y. Liu, S.-H. Bae, H.J. Kim et al., Direct light pattern integration of low-temperature solution-processed all-oxide flexible electronics. ACS Nano 8(9), 9680– 9686 (2014). https://doi.org/10.1021/nn504420r

- D. Li, M. Zhao, K. Liang, H. Ren, Q. Wu et al., Flexible low-power source-gated transistors with solution-processed metal-oxide semiconductors. Nanoscale 12(42), 21610– 21616 (2020). https://doi.org/10.1039/D0NR06177H

- S. Chung, K. Cho, T. Lee, Recent progress in inkjet-printed thin-film transistors. Adv. Sci. 6(6), 27 (2019). https://doi. org/10.1002/advs.201801445

- F. Shao, Q. Wan, Recent progress on jet printing of oxidebased thin film transistors. J. Phys. D Appl. Phys. 52(14), 143002 (2019). https://doi.org/10.1088/1361-6463/aafd79

- S. Conti, L. Pimpolari, G. Calabrese, R. Worsley, S. Majee et al., Low-voltage 2D materials-based printed field-effect transistors for integrated digital and analog electronics on paper. Nat. Commun. 11(1), 3566 (2020). https://doi.org/10. 1038/s41467-020-17297-z

- K. Fukuda, T. Someya, Recent progress in the development of printed thin-film transistors and circuits with high-resolution printing technology. Adv. Mater. 29(25), 1602736 (2017). https://doi.org/10.1002/adma.201602736

- 20. T. Sekitani, T. Yokota, K. Kuribara, M. Kaltenbrunner, T. Fukushima et al., Ultraflexible organic amplifier with

biocompatible gel electrodes. Nat. Commun. **7**(1), 11425 (2016). https://doi.org/10.1038/ncomms11425

- P.J. Yunker, T. Still, M.A. Lohr, A.G. Yodh, Suppression of the coffee-ring effect by shape-dependent capillary interactions. Nature 476(7360), 308–311 (2011). https://doi.org/10. 1038/nature10344

- J. Jang, H. Kang, H.C.N. Chakravarthula, V. Subramanian, Fully inkjet-printed transparent oxide thin film transistors using a fugitive wettability switch. Adv. Electron. Mater. 1(7), 1500086 (2015). https://doi.org/10.1002/aelm.20150 0086

- X. Shen, C.-M. Ho, T.-S. Wong, Minimal size of coffee ring structure. J. Phys. Chem. B 114(16), 5269–5274 (2010). https://doi.org/10.1021/jp912190v

- R.D. Deegan, O. Bakajin, T.F. Dupont, G. Huber, S.R. Nagel et al., Capillary flow as the cause of ring stains from dried liquid drops. Nature 389(6653), 827–829 (1997). https://doi. org/10.1038/39827

- R.D. Deegan, Pattern formation in drying drops. Phys. Rev. E 61(1), 475–485 (2000). https://doi.org/10.1103/PhysRevE.61. 475

- 26. J. Leppäniemi, K. Eiroma, H. Majumdar, A. Alastalo, Far-UV annealed inkjet-printed In<sub>2</sub>O<sub>3</sub> semiconductor layers for thinfilm transistors on a flexible polyethylene naphthalate substrate. ACS Appl. Mater. Interfaces 9(10), 8774–8782 (2017). https://doi.org/10.1021/acsami.6b14654

- Y. Li, L. Lan, S. Sun, Z. Lin, P. Gao et al., All inkjet-printed metal-oxide thin-film transistor array with good stability and uniformity using surface-energy patterns. ACS Appl. Mater. Interfaces 9(9), 8194–8200 (2017). https://doi.org/10.1021/ acsami.7b00435

- Y. Li, L. Lan, S. Hu, P. Gao, X. Dai et al., Fully printed topgate metal–oxide thin-film transistors based on scandiumzirconium-oxide dielectric. IEEE Trans. Electron Dev. 66(1), 445–450 (2019). https://doi.org/10.1109/TED.2018.2877979

- A. Zeumault, S. Ma, J. Holbery, Fully inkjet-printed metaloxide thin-film transistors on plastic. Phys. Status Solidi A 213(8), 2189–2195 (2016). https://doi.org/10.1002/pssa.20160 0077

- P. Canhola, N. Martins, L. Raniero, S. Pereira, E. Fortunato et al., Role of annealing environment on the performances of large area ITO films produced by RF magnetron sputtering. Thin Solid Films 487(1–2), 271–276 (2005). https://doi.org/ 10.1016/j.tsf.2005.01.078

- J. Zhang, J. Wilson, G. Auton, Y. Wang, M. Xu et al., Extremely high-gain source-gated transistors. Proc. Natl. Acad. Sci. USA 116(11), 4843–4848 (2019). https://doi.org/ 10.1073/pnas.1820756116

- S. Li, M. Tian, Q. Gao, M. Wang, T. Li et al., Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18(10), 1091–1097 (2019). https://doi.org/10. 1038/s41563-019-0455-8

- 33. Y. Wang, Z. Wang, K. Huang, X. Liang, C. Liu et al., Solution-processed ITO thin-film transistors with doping of gallium oxide show high on-off ratios and work at 1 mM drain voltage. Appl. Phys. Lett. **116**(14), 141604 (2020). https://doi.org/10.1063/1.5141140

- 34. Y. Le, Y. Shao, X. Xiao, X. Xu, S. Zhang, Indium-tin-oxide thin-film transistors with in situ anodized Ta<sub>2</sub>O<sub>5</sub> passivation layer. IEEE Electron. Device Lett. **37**(5), 603–606 (2016). https://doi.org/10.1109/LED.2016.2548785

- A. Lu, J. Sun, J. Jiang, Q. Wan, Microporous SiO<sub>2</sub> with huge electric-double-layer capacitance for low-voltage indium tin oxide thin-film transistors. Appl. Phys. Lett. **95**(22), 222905 (2009). https://doi.org/10.1063/1.3271029

- T. Kamiya, K. Nomura, H. Hosono, Origins of high mobility and low operation voltage of amorphous oxide TFTs: Electronic structure, electron transport, defects and doping. J. Disp. Technol. 5(7), 273–288 (2009). https://doi.org/10.1109/jdt.2009.2021582

- A. Lyubchyk, A. Vicente, B. Soule, P.U. Alves, T. Mateus et al., Mapping the electrical properties of ZnO-based transparent conductive oxides grown at room temperature and improved by controlled postdeposition annealing. Adv. Electron. Mater. (2016). https://doi.org/10.1002/aelm.201500287

- H. Faber, S. Das, Y.-H. Lin, N. Pliatsikas, K. Zhao et al., Heterojunction oxide thin-film transistors with unprecedented electron mobility grown from solution. Sci. Adv. 3(3), e1602640 (2017). https://doi.org/10.1126/sciadv.1602640

- Y.-H. Lin, H. Faber, J.G. Labram, E. Stratakis, L. Sygellou et al., High electron mobility thin-film transistors based on solution-processed semiconducting metal oxide heterojunctions and quasi-superlattices. Adv. Sci. 2(7), 1500058 (2015). https://doi.org/10.1002/advs.201500058

- J.S. Heo, S.-P. Jeon, I. Kim, W. Lee, Y.-H. Kim et al., Suppression of interfacial disorders in solution-processed metal oxide thin-film transistors by Mg doping. ACS Appl. Mater. Interfaces 11(51), 48054–48061 (2019). https://doi.org/10.1021/acsami.9b17642

- S.N. Luo, A. Kono, N. Nouchi, F. Shoji, Effective creation of oxygen vacancies as an electron carrier source in tin-doped indium oxide films by plasma sputtering. J. Appl. Phys. 100(11), 113701 (2006). https://doi.org/10.1063/1.2372571

- J. Jeong, G.J. Lee, J. Kim, J. Kim, B. Choi, Oxygen dispersive diffusion induced bias stress instability in thin active layer amorphous In–Ga–Zn–O thin-film transistors. Appl. Phys. Express. 6(3), 031101 (2013). https://doi.org/10.7567/apex.6.031101

- W. Wang, L. Li, C. Lu, Y. Liu, H. Lv et al., Analysis of the contact resistance in amorphous InGaZnO thin film transistors. Appl. Phys. Lett. (2015). https://doi.org/10.1063/1.49286 26

- 44. S.Y. Lee, J. Kim, A. Park, J. Park, H. Seo, Creation of a shortrange ordered two-dimensional electron gas channel in Al<sub>2</sub>O<sub>3</sub>/ In<sub>2</sub>O<sub>3</sub> interfaces. ACS Nano **11**(6), 6040–6047 (2017). https:// doi.org/10.1021/acsnano.7b01964